**Electronique 2009 - 2010**

### ELECTRONIQUE NUMERIQUE

**CORRIGES**

EISTI Guy Almouzni

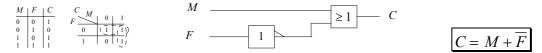

## Corrigé TD Electronique n' 10 | TAlgebre de Boole - Logique Combinatoire M

TD1 Logique Combinatoire1

**主共X**统

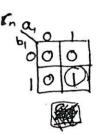

| BA | 0 | 1  |       |

|----|---|----|-------|

| 0  | 1 | 0  |       |

| 1  | 0 | 0  |       |

|    | ζ | ĀB | = A+B |

$$e) NOR: A,B \rightarrow \overline{A+B}$$

$$A \longrightarrow \overline{A}$$

$$\overline{A+B}$$

### TD 1 CORRIGE. LOGIQUE COMBINATOIRE 1

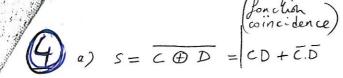

### 4. Synthèse d'un système logique combinatoire

### 5. Synthèse d'une Fonction logique

d'où:

$$s = \overline{abc} + a\overline{bc} + ab\overline{c} + abc$$

Simplification de S:

- algébrique :

$$s = c(\overline{a}b + a\overline{b}) + abc = c(a \oplus b) + abc$$

- graphique (Karnaugh) :

$$s = ab + bc + ab$$

### 6. Réalisation d'une fonction logique à l'aide de portes NAND exclusivement

TD 1 Corrigé. 1

### TD 1 ANNEXE CORRIGE. LOGIQUE COMBINATOIRE 1

### 1. Analyse d'un système logique combinatoire

- Expression de S:  $S = (\overline{a_0 \oplus b_0}).(\overline{a_1 \oplus b_1}).(\overline{a_2 \oplus b_2}).(\overline{a_3 \oplus b_3})$

ou:  $S = (a_0 \odot b_0).(a_1 \odot b_1).(a_2 \odot b_2).(a_3 \odot b_3)$

- Rôle du montage comparateur :

Détecter l'égalité des 2 mots binaires de 4 bits :  $A = a_3 a_2 a_1 a_0$  et :  $B = b_3 b_2 b_1 b_0$

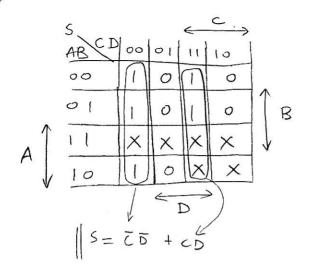

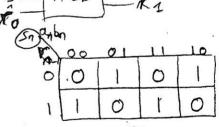

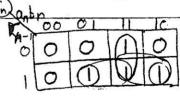

### 2. Simplification d'une fonction logique

| S $CD$ $AB$ | 00 | 01 | 11  | 10       |

|-------------|----|----|-----|----------|

| 00          | 0  | 0  | 1   | 1        |

| 01          | 1  | 1  | 0   | 0        |

| 11          | X  | X  | X   | X        |

| 10          | 0  | 0  | / X | <u>X</u> |

S = BC + BC

$S = B \oplus C$

TD 1 Corrigé.

### TP 1 CORRIGE. LOGIQUE COMBINATOIRE 1

### 4. Etude Expérimentale

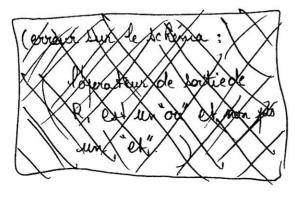

#### 4.3. Facultatif - Réalisation d'une fonction logique à l'aide de portes NOR exclusivement

TP 1 Corrigé.

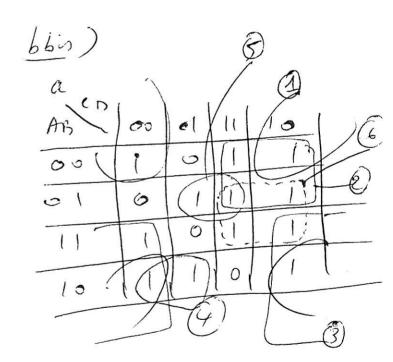

30 Il seule

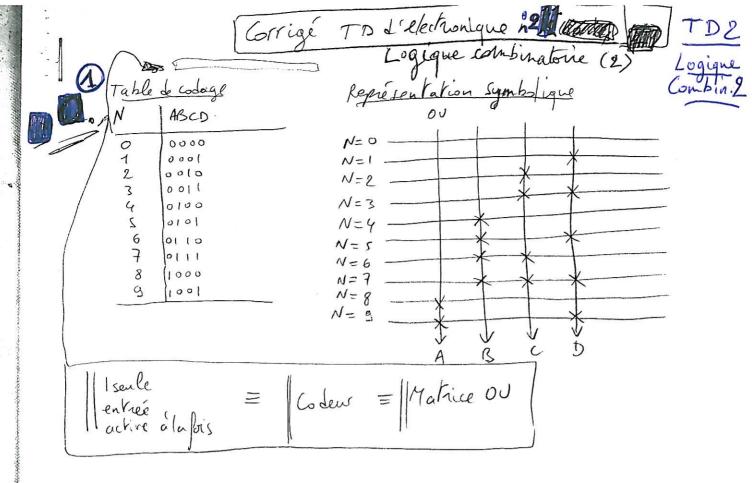

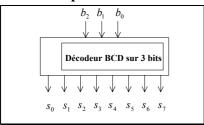

table de Décodage

Sec.

Representation Symbolique

(5) Multiplier par 2 = Décaler le mot binaire vers la ganche droite

Diviser par 2 = this time de la partie d

NXZ

b.2 = 2xb2'

Les bit intiduit pur décalage étant à 0.

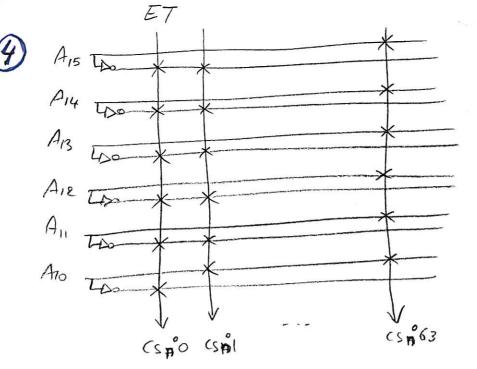

Par besoin de faire la table de transcocage, il suffer de prendre les bits

décalés de 1 cran:

(MSB-)A S Y = B C Z = C

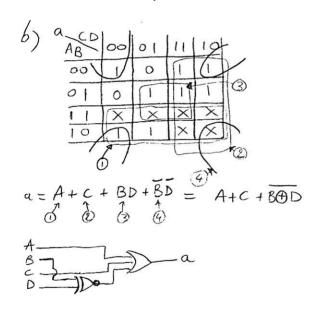

o) iden gre skis(1) 7.

mars les 6 dernières

ligner sont indéfinles (x)

pour a b c de J

| 102000 40 |           |     |                                         |

|-----------|-----------|-----|-----------------------------------------|

| A         | B         | CD  | abcdegg                                 |

| 0 0       | 0         | 00  | 111110                                  |

|           | ide       | m — | iden -                                  |

| 91        | 0         | 0 1 | 1111011                                 |

| ABCDE     | 0 0 1 1 1 | 10  | ××××××<br>×××××××<br>×××××××<br>××××××× |

|   |     | (  | 6) |    | , ,  |   | `        |    |   |    |    |    |     | ,    |

|---|-----|----|----|----|------|---|----------|----|---|----|----|----|-----|------|

|   | 4   |    | NI | BC | ebu. | ) | ۶.<br>پر |    |   | /  | 11 | 75 | egn | ents |

|   | · N | TA | B  | C  |      |   | a        | 10 | c | 1  | le | TP | 19  | 1    |

|   | 0   | 0  | 0  | 0  | 0    |   | 1        | 1  | 1 | -1 | 1  | Ti | 6   | 1    |

|   | 1   | 0  | 0  | 0  | 11   | 4 | 0        | 1  | 1 | 0  | 0  | 0  | 0   | -    |

|   | 2   | 0  | 0  | 1  | 0    |   | 1        | 1  | 0 | 1  | 1  | 0  |     | 1    |

|   | 13  | 0  | 0  | 1  | 1    |   | 1        | 1  | 1 | 1  | 0  | 0  | 1   | l    |

|   | 3   | 0  | Ti | 0  | 0    | 1 | 0        | 1  | 1 | O  | 0  | 1  |     |      |

|   | 15  | 0  | 1  | 0  | 1    | 1 | 1        | 0  | l | i  | 0  | 1  | 1   |      |

|   | 6   | 0  | 1  | 1  | 0    |   | 1        | 0  | 1 | 1  | 1  | 1  | 1   |      |

|   | 7   | 0  | -  | 1  | 1    | İ | 1        | 1  | 1 | 0  | 0  | 0  | 0   |      |

|   | 8   | 1  | 0  | 0  | 0    | T | 1        | ł  | 1 | 1  | 1  | 1  | 1   |      |

| Į | 3   |    | 0  | O  | 1    | 1 | 1        | 1  | 1 | 1  | 0  | 1  | 1   |      |

| 1 | Á   | 1  | 0  | (  | U    | 1 | 1        | 1  | 1 | 0  | 1  | 1  | 1   |      |

| 1 | B   | 1  | 0  | 1  |      | - | 0        | 0  | 1 | 1  | 1  | 11 | Ī   | 16   |

| 1 | C   |    | 1  | 0  | 0    | T | 1        | 0  | 0 | 1  | 11 | 11 | 0   |      |

| 1 | ۵   | 1  | 1  | 0  | 1    |   | 0        | I  | 1 | 1  | 1  | 0  | 1   |      |

| - | E   |    | 1  | 7  | 0    |   | 1        | 0  | Э | 1  | 1  | 1  |     |      |

| 1 | F   |    | 1  | 1  | 1    |   | 1        | 0  | ٥ | 0  | 1  |    | 1   |      |

P. State of

B= b, b, b, b

23 B 2 B 1 BO

78

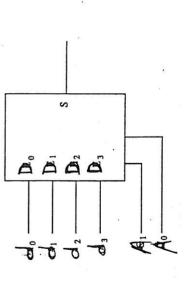

selection

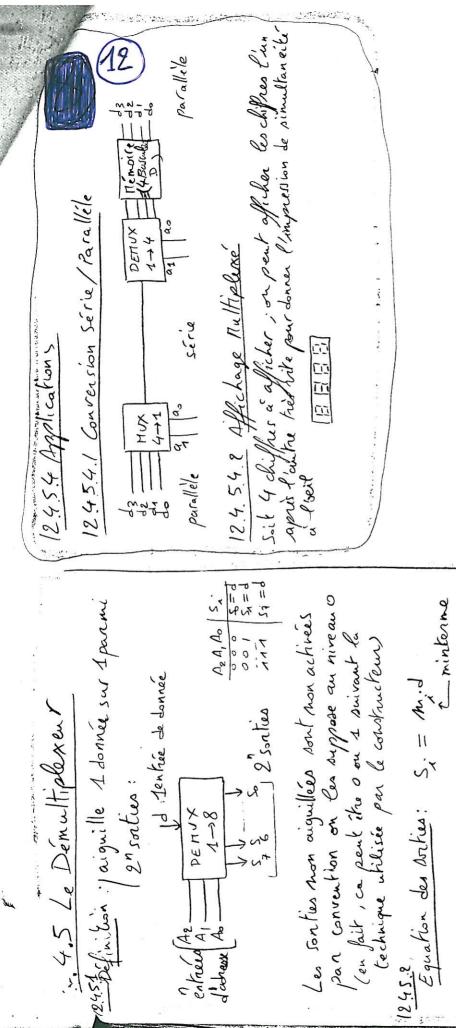

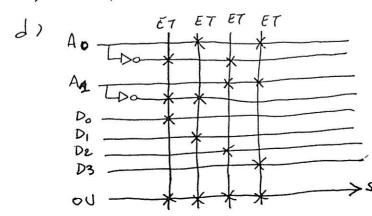

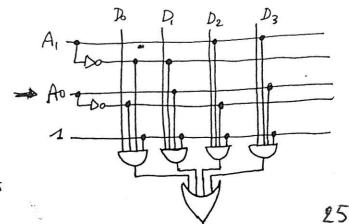

Soit un mot binaire  $D = d_3 d_2 d_1 d_0$  disponible en mode parallèle, c'est-à-dire sur quatre sils, chaque sil étant affecté à un élément binaire du

Jonversion parallèle-série

et enfin d3. Ceci revient à sélectionner (ou à aiguiller) l'un des éléments binaires de Dsur le fil unique de sortie série. Le multiplexeur est capable Pour transmettre les éléments binaires en série, c'est-à-dire les uns à la suite des autres sur un seul fil, il faut d'abord transmettre d, puis d, puis d2 d'essectuer cette tâche si les combinaisons correspondantes sont placées successivement sur les commandes de sélection.

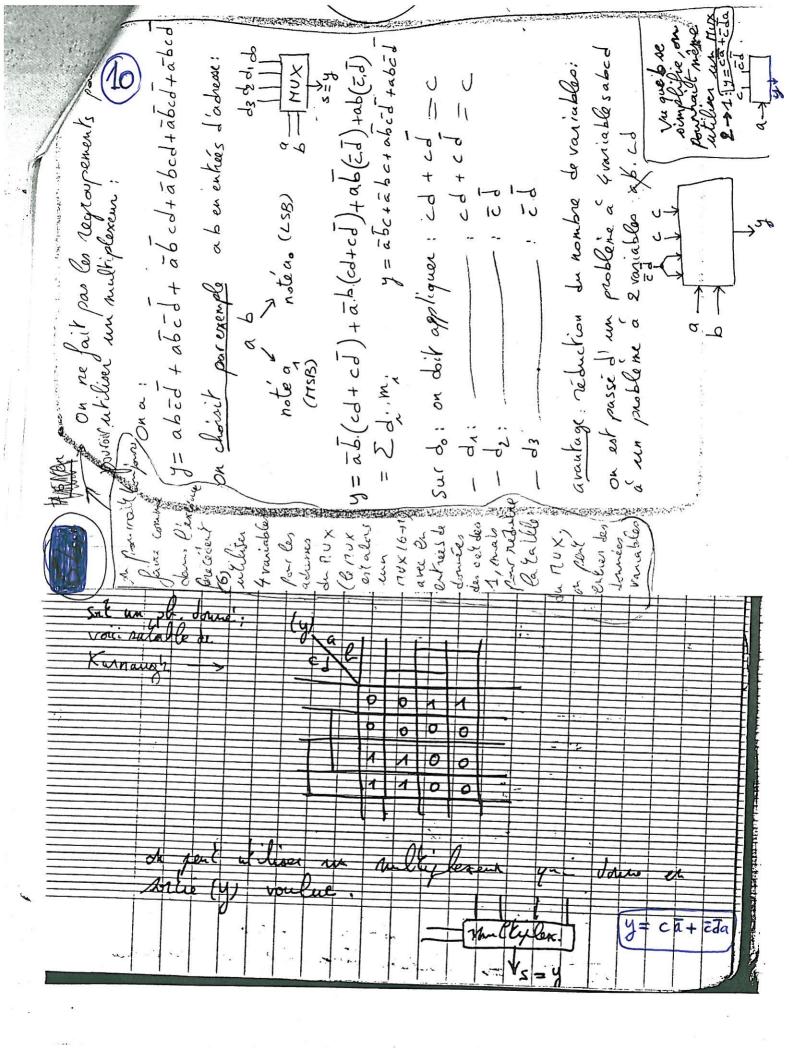

E Génération de fonctions

Toute fonction logique combinatoire peutse mettre sous forme canonique (cf. § 2.2.1, théorèmes d'expansion de Shannon). Par exemple, une fonction de deux variables A et B se développe suivant l'expression

= ; et  $A(B) = \overline{A} \overline{B} f(0,0) + \overline{A} \overline{B} f(0,1) + A \overline{B} f(1,0) + A B f(1,1)$ est la valeur particylière de la fonction logique lorsque où =

Un multiplexeur's quatre entrées, donc deux commandes, délivre une ie S reliée aux commandes C1 Co par la relation sort

et //A,B), C, et A, C, et B, les valeurs des batrées du martiplexeur et celles de la fonction. En comparant les deux relations précédentes, il es Nacile de voir qu'il ossible de réaliser toutes les fonctions de deux variables en identifiant S  $\leftarrow C_1C_0E_3$ 4 C1C6E2 S = C1 Co Eo + C1 Co Ex est

Les entrées de sélection du multiplexeur sont alors les variables de la sondtion, et les entrées du multiplexeur permettent de sèlectionner la sonction à réaliser.

19 Jentie de donnée

DE 11 1X

entrava A1

s s s s saties

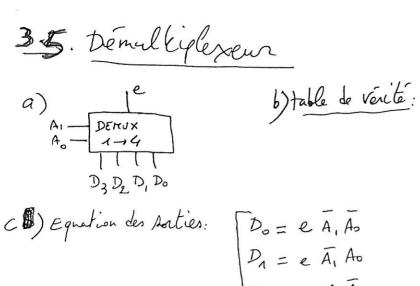

4.5 Le Démultiplaxent

(Représentation) Symbolique 12453 Realisation;

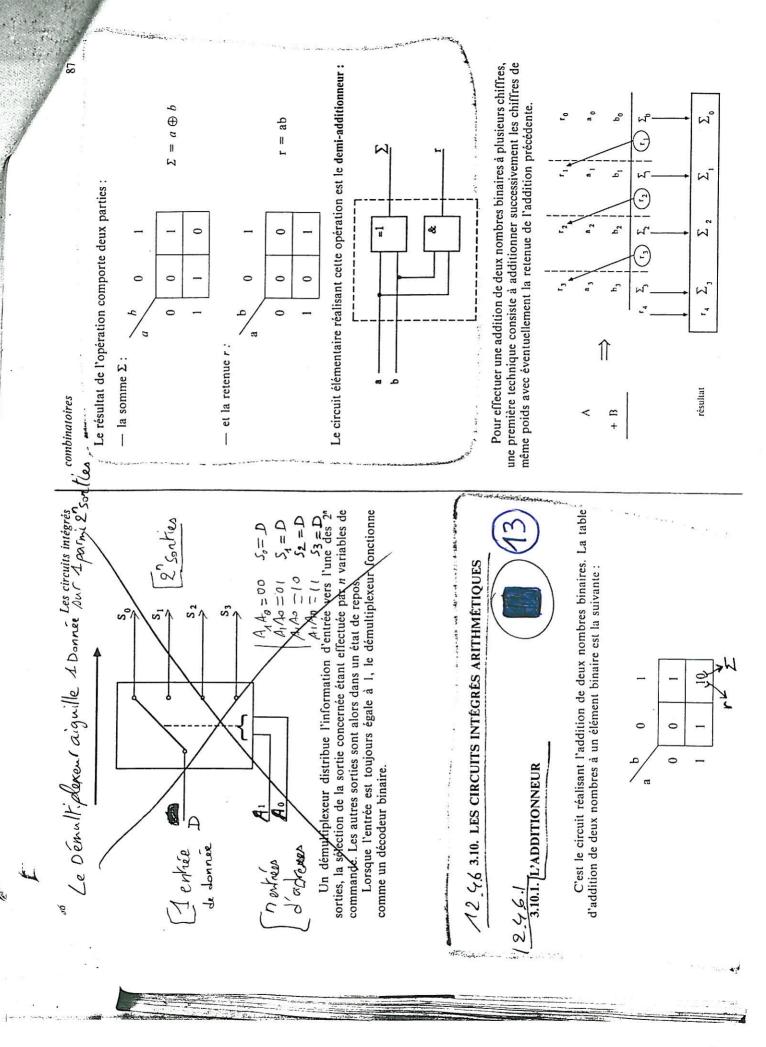

Les circuits intégrés

combinatoires

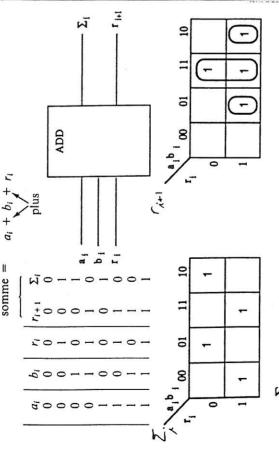

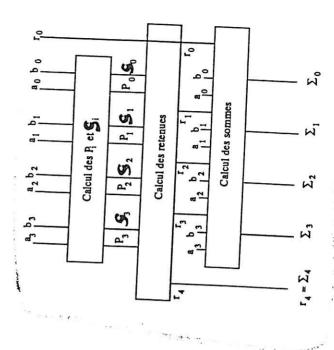

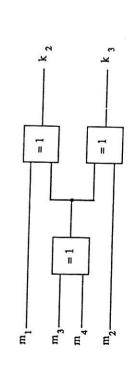

La structure de l'additionneur de deux nombres est alors répétitive. Une cellule élémentaire peut donc être utilisée pour chaque poids. Elle est appelée additionneur complet. L'addition globale est réalisée par la mise en cascade des cellules au sens des retenues.

L'additionneur complet est défini par la table de vérité ci-après :

W

Cette solution est intéressante d'un point de vue du matériel parce que répétitive. Par contre, comme le résultat d'une addition ne peut pas être obtenu instantanément, le temps maximum mis pour obtenir le résultat est directement proportionnel au nombre d'additionneurs. En effet, après le premier temps de calcul la retenue  $r_1$  est appliquée au second additionneur. Ce n'est qu'après le second temps de calcul que la retenue  $r_2$  est délivrée et ainsi de suite, jusqu'au dernier additionneur. Pour cette raison, l'addition ainsi réalisée porte le nom d'« additionneur à propagation de la retenue » ou « additionneur à retenue série ».

toutes les retenues en parallèle, directement à partir des données sans même calculer les sommes partielles. Le circuit ainsi réalisé est alors appelé « additionneur à retenue anticipée ».

En reprenant le tableau de Karnaugh relatif au calcul de la retenue il vient :

$r_{i+1} = a_i b_i + r_i (a_i + b_i)$

$r_{i+1} = a_i b_i + r_i (a_i \oplus b_i)$

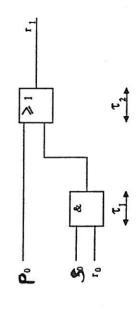

Ce qui donne le schéma:

= a + + b + F

Afin d'éviter des temps de calcul cumulatifs, il ne faut pas utiliser la relation en tant que relation de récurrence, c'est-à-dire qu'il ne faut pas utiliser un résultat de calcul pour le calcul suivant. Il faut systématiquement recalculer chaque terme, ce qui donne en posant  $S_i = a_i + b_i$  et  $P_i = a_i b_i$ :

E

L'addition de deux nombres de n éléments binaires nécessite n additionneurs complets, la retenue appliquée sur les plus faibles poids est nulle et chaque retenue calculée est appliquée au chiffre de poids immédiatement

13

supérieur.

combinatoires

Les circuits intégrés

**拉斯**森市

Et ainsi de suite:

$r_2 = P_1 + r_1 S_1 = P_1 + (P_0 + r_0 S_0) S_1$  $r_2 = P_1 + P_0 S_1 + r_0 S_0 S_1$

De même:

25

7.4

·#.

$$r_3 = P_2 + r_2 S_2 = P_2 + (p_1 + p_0 S_1 + r_0 S_0 S_1) S_2$$

$$= P_2 + p_1 S_2 + r_0 S_0 S_1 S_2$$

$r_4 = p_3 + r_3 S_3$ =  $p_3 + p_2 S_3 + p_1 S_2 S_3 + p_0 S_1 S_2 S_3 + r_0 S_0 S_1 S_2 S_3$

On constate que les temps de calcul des retenues sont tous égaux. Ils correspondent au temps de transit de l'information dans une porte ET  $(\tau_1)$  pas son temps de transit).

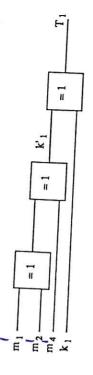

La structure d'un additionneur quatre éléments binaires utilisant la technique de calcul anticipé des retenues est la suivante:

£

સ

25

ď

ه که

å

1

~

જ

Afin d'illustrer le gain apporté par le principe de la retenue anticipée, le de formats donne les temps de calcul pour une addition de deux nombres

-menalen de Parife On appelle n. Les circuits intégrés

92

| Temps de calcul en nS (logique TTL série N) |                                 | avec un additionneur 4 bits intégrés | avec utilisation d'un généra-<br>teur de retenue | avec deux générateurs de retenue en cascade |

|---------------------------------------------|---------------------------------|--------------------------------------|--------------------------------------------------|---------------------------------------------|

| ul en nS (logic                             | Retenue<br>anticipée            | 24                                   | 36                                               | , 09                                        |

| Temps de calc                               | Propagation<br>de la<br>retenue | 24                                   | 36<br>48<br>60                                   | 192                                         |

| Format                                      | de chaque<br>nombre<br>en bits  | 4 0                                  |                                                  | 40                                          |

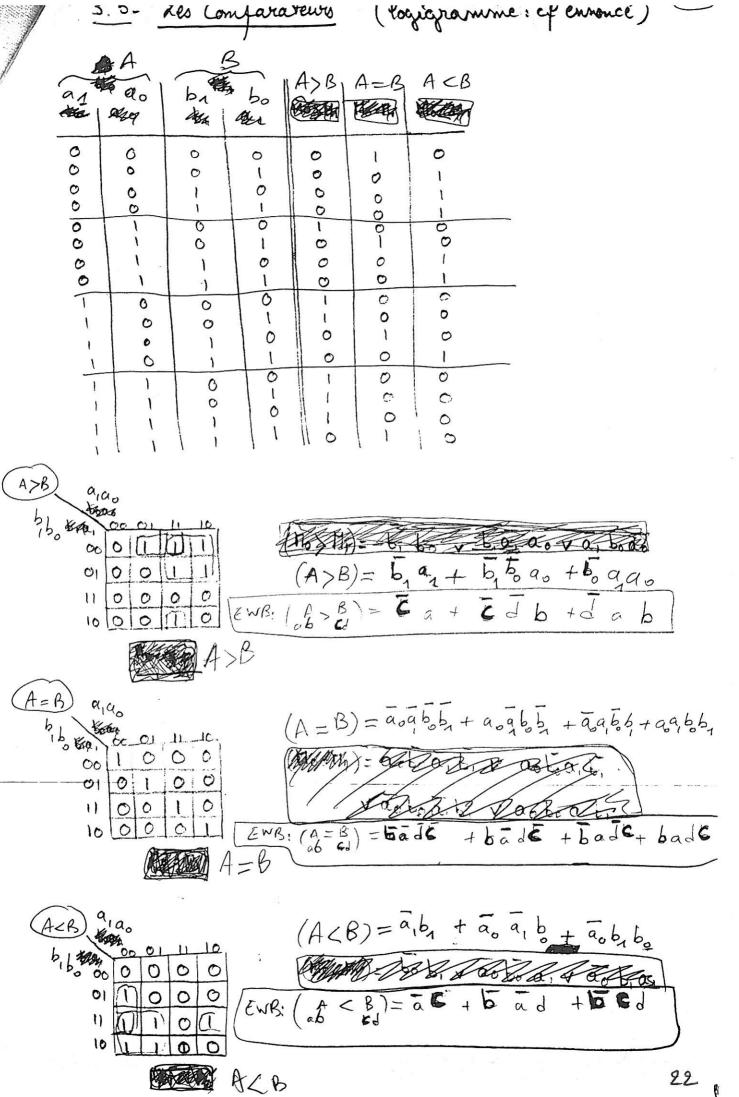

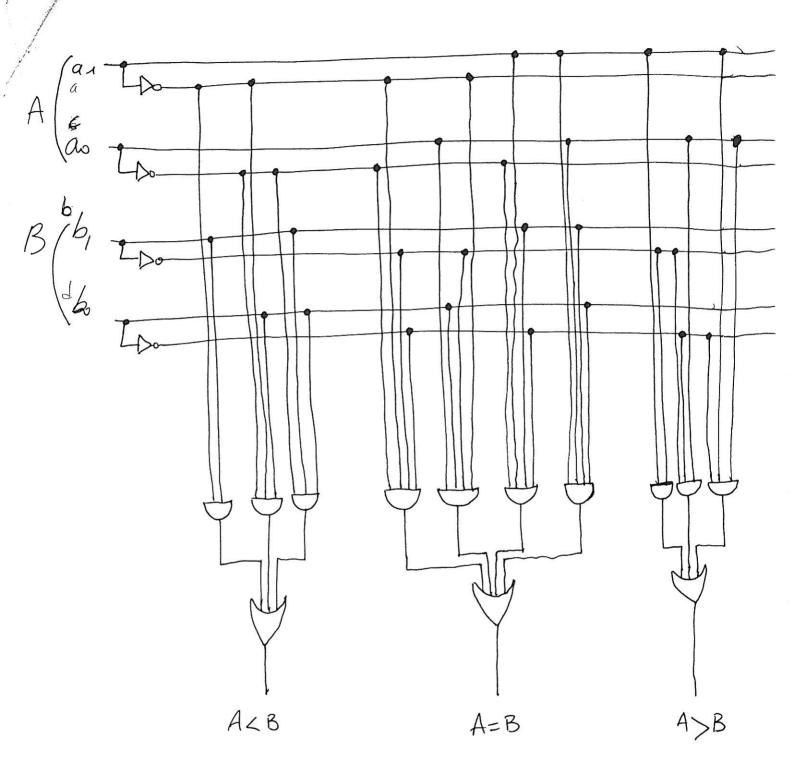

nombres et éventuellement d'indiquer le nombre le plus grand ou le plus Un comparateur est un dispositif capable de détecter l'égalité de deuxlatole en con I + arithmet 1110=1+0110 12.462 Soustraction Por Se ramene a LE COMPARATEUR

Principe

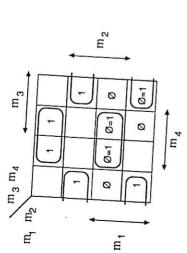

Pour effectuer la comparaison de deux nombres, deux techniques sont couramment utilisées :

La soustraction des deux nombres. Si le résultat de l'opération A-Best positif, cela signifie que A est supérieur à B. Si le résultat est nul, les deux nombres sont égaux.

la plupart des circuits intégrés commercialisés. La comparaison s'effectue - Une comparaison bit à bit. C'est cette méthode qui est utilisée dans poids à poids en commençant par le chiffre le plus significatif.

supérieur à B si son élément binaire le plus significatif (MSB) est supérieur à celui de B. Si ces deux éléments binaires sont égaux, la supériorité (ou l'insériorité) ne peut être déterminée que par l'examen des bits de poids Les nombres A et B ayant le même format, le nombre A est forcément immédiatement inférieur et ainsi de suite.

L'examen des poids successifs s'arrêle dès que l'un des éléments binaires est supérieur ou inférieur à l'autre. Les deux nombres A et B sont égaux si, après avoir examiné tous les éléments binaires, il n'a pas été détecté de supériorité ou d'infériorité.

combinatoires

# Comparateur donnant l'égalité de deux nombres

les chiffres sont égaux deux à deux. Pour détecter l'égalité de deux éléments binaires, un opérateur OU exclusif complémenté est indispensable. Un C'est le comparateur le plus simple. Deux nombres sont égaux si tous opérateur ET indique la simultanéité de toutes les inégalités partielles.

de quatre éléments binaires chacun, Soient deux nombres A et  $A = a_3a_2a_1a_0$  et  $B = b_3b_2b_1b_0$ :

=  $B \text{ si } (A_3 = b_3) \text{ ET } (a_2 = b_2) \text{ ET } (a_1 = b_1) \text{ ET } (a_0 = b_0)$

Ce qui donne le schéma :

A = B

# Comparateur complet

Par analogie avec l'additionneur, la conception d'un comparateur complet pour des nombres de quatre éléments binaires peut se saire de deux façons différentes. - Première solution: En cascade, c'est-à-dire avec propagation des égalités pautielles. Les poids de A et de B sont comparés en commençant par le plus élevé. La comparaison sur les poids faibles ne peut être faite que si tous les bits de poids plus élevés sont égaux deux à deux.

atb= ab +ab= acb rapped: 1 a + a b + a b O le mot a sume parite parse n'e nombre de l'est pair. You de vendre les hanominions nérique plus robustes au bruit, or adjoint sur bit à tous les mots trausmis. Le bit, dit de parilé est doir de façon à coque le mot complet forme du mot et du bit de parité sort pala Ritz Parite Genére Le principe utilier pour générer ce bit de parité rapise sur la propriété du 00 on appelle parite of un mot binaire of le mombre de 1 contemus dans ce mot 12.4 6.4. Généraleur de Parité

)话:

( Dectamoiatif) = M2 (m, mo + m, mo) + m2 (m, mo + m, mo) = mg (mo @ mi) + mg (mo @ mi) Mo & M & ME 11 ×

Solution des

a de la constante de la consta

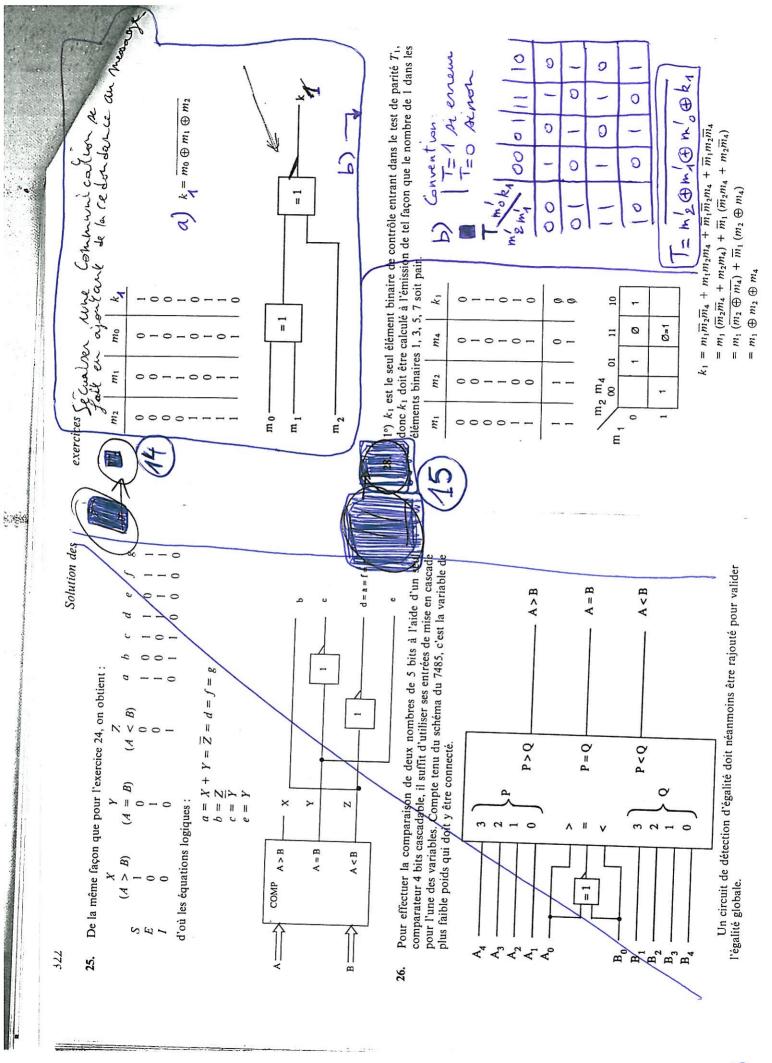

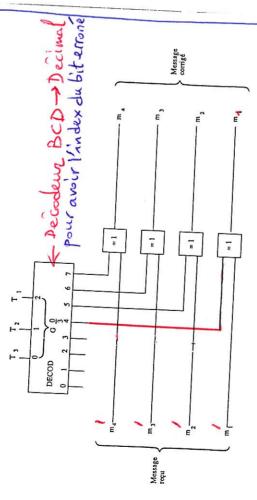

Autre solution k, dépend des quatre élèments binaires du message. Le tableau de Karnaugh correspondant est rempli à partir du code de Hamming.

$k_1 = m_1 \overline{m}_2 \overline{m}_4 + m_1 m_2 m_4 + \overline{m}_1 m_2 \overline{m}_4 + \overline{m}_1 \overline{m}_2 m_4$   $k_1 = m_1 \oplus m_2 \oplus m_4$

k2 résulte du test de parité sur les éléments binaires 3. 6. 7. d'où :

exercices

2°) Il y a deux solutions:

a) Fabriquer  $k_1$  à partir de  $m_1$ ,  $m_2$  et  $m_4$  et comparer avec  $k_1$  reçu de façon que  $T_1=0$  si  $k_1=k_1'$  (et  $T_1=1$  si  $k_1=k_1'$ ); d'où le schéma :

b) Calculer  $T_1$  à partir des diffèrentes possibilités de  $m_1m_2m_4k_1$  (eb 1, 3, 5 et 7).

|                     |                                     |      | 2              |                                              | 325 |

|---------------------|-------------------------------------|------|----------------|----------------------------------------------|-----|

|                     |                                     |      | Y Tal          | N. A. S. |     |

|                     |                                     |      | ***            |                                              | _   |

|                     |                                     |      | Y at           | The course was                               | -   |

|                     |                                     |      | ž              |                                              |     |

|                     |                                     |      | A              | Marine Marine TA                             | _   |

|                     |                                     |      |                | 1                                            |     |

|                     |                                     |      | 8              | man - land                                   | Ξ   |

|                     | .5                                  | Z    | 1. 1.          | A                                            | =   |

|                     | pair<br>impair                      | myma |                |                                              |     |

|                     | nombre de 1 pair<br>nombre de 1 imp |      |                |                                              |     |

|                     | e e                                 |      |                |                                              |     |

|                     | 5 5                                 |      |                |                                              |     |

|                     | 五百                                  |      | ž.             |                                              |     |

|                     | 1 5 5                               |      | ar Year        | . Ye we see                                  | =   |

| 7,                  | 00                                  | -00  | Visit Services |                                              | -   |

| 4                   |                                     |      | En . In.       | · hme                                        | -   |

| 114                 | 0                                   | 0-0  | -              |                                              | _   |

| ,<br>m <sub>2</sub> | 00                                  | 00-  | C Y"           |                                              | _   |

|                     |                                     |      |                |                                              | _   |

| 1111                | 0000                                | ·    | - L. h. L.     | The second second                            | -   |

| $K_1$               | 0000                                | 000  | C v v          | To the me                                    | _   |

| ~                   |                                     |      |                |                                              |     |

|                     |                                     |      |                |                                              |     |

Ici toutes les combinaisons sont prévues. Certaines sont impossibles s'il n'y a qu'une seule erreur. Les 1 placés en diagonale indiquent une solution comportant des OU exclusifs.

$$T_1 = k_1 \oplus m_1 \oplus m_2 \oplus m_4$$

$$T_2 = m_1 \oplus m_3 \oplus m_4 \oplus k_2$$

De même

$$T_3 = m_2 \oplus m_3 \oplus m_4 \oplus k_3$$

No.

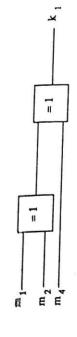

Le schéma est identique à celui de l'émetteur auquel on ajoute trois OU exclusifs.

$3^{\circ}$ )  $(T_3T_2T_1)_2$  indique le numéro de l'élément binaire erroné, donc celui qu'il saut corriger. La correction consiste simplement à changer l'élément binaire faux à l'aide d'un circuit complément.

Le OU exclusif permet d'être soit un circuit transparent soit un circuit inverseur suivant sa commande.

Il n'est pas utile de corriger les éléments de contrôle.

Cc = 0 = pro dimerium de b ; c=1 = jiverium du bit b), on utilise un circuit overcluig. Rapped: Pour inverser un bit 6 selor une commande c

$$\sqrt{z4}$$

$= 5 = b\theta c = 6c + 5c$

$|c=0: s=b|$

# Bibliographie

Boole G., The Mathemalical Analysis of Logic, Çambridge (réédité par Blackwell,

Boole G., An Investigation of the Laws of Thought, Londres (réédité par Dover

Karnaugh M., «The Map Method of Synthesis of Combinational Logic Circuits », Communications and Electronics, n° 9, November 1953, p. 593-599.

McCluskey E.J. Jr., « Minimization of Boolean Functions », Bell System Technical

Journal, vol. 35, November 1958, p. 14/7-1444.

Techniques for Computing Systems Spartan Books Co. 1962, p. 9-46. McCluskey E.J. Jr., Introduction to the Theory of Switching, McGraw-Hill Book Co, McCluskey E.J. Jr., « Transients in Combinational Logic Circuits », Redundancy

McCluskey E.J. Jr. and Bartee T.C., A Survey of Switching Circuits Theory, McGraw-Hill Book Co, New York, 1962.

McCluskey E.J. Jr. and Schor, H., « Essential Multiple Output Prime Implicants », Proceeding of the Symposium on the Mantematical Theory of Automata, 1962,

Polytechnic Press of the Polytechnic Institute of Brooklyn, New York, p. 437-457. Quine W.V., « The Problem of Simplifying Truth Functions », Am. Math. Monthly,

Quine W.V.. « A Way to Simplify Truth Functions », Am. Math. Monthly, vol. 62,

November 1955, p/627-631. Quine W.V., «On Cores and Prime Implicants of Truth Functions », Am. Math. Monthly, vol. 6\,\varepsilon\, November 1959, p. 755-760.

Shannon C.E., «A Symbolic Analysis of Relay and Switching Circuits », Transactions of the AIEE/vol. 57, 1938, p. 713-723.

Shannon C.E., « The Synthesis of Two-Terminal Switching Circuits », Bell System Tison P., & Recherche de termes premiers d'une sonction booléenne, », Automatisme, Technical/Journal, vol. 28, 1949, p. 59-98.

f. Théorie des consensus et algorithmes de recherche des bases premières, Colloque d'algèbre de Boole, Grenoble, janvier 1965. tome JK, nº 1, janvier 1964. Tison P

fison P., « Algèbre booléenne : théorie des consensus. Recherche des bases premières d'une fonction booléenne », Automatisme, tome X, n° 6, juin 1965.

leith E.W., « A Chart Method for Simplifying Truth Functions », Proc. ACM, May

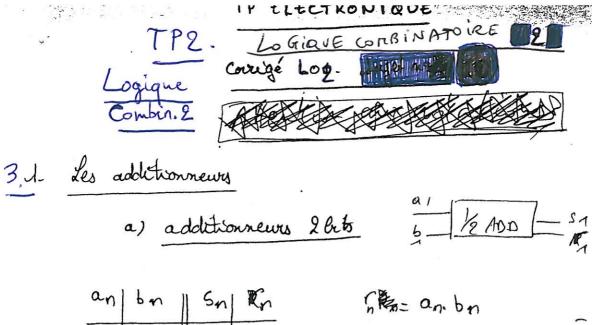

### **TD 2 CORRIGE. LOGIQUE COMBINATOIRE 2**

Transmission

### 3. Construction d'un code détecteur d'erreur

$$a) \ k_1 = \overline{m_2 \oplus m_1 \oplus m_0}$$

b)

$$d = \overline{m'_1 \oplus m'_1 \oplus m'_0 \oplus k_1}$$

TD 2 Corrrigé.

| an | bn | Sn | Kn |

|----|----|----|----|

| G  | 0  | 0  | 0  |

| 0  | 1  | 1. | 0  |

| 1  | 0  | 1  | 0  |

| 1  | 1  | 0  | 1  |

|    |    |    |    |

| She and |                        |

|---------|------------------------|

| Sn=and  | bn car = a, b, + a, b, |

| 70 1    | En a                   |

| 6) | additionneur | 3 | ato |

|----|--------------|---|-----|

|    |              |   |     |

| an | bn             | <b>6</b> 6 | Sn  | <b>B</b> (1) |

|----|----------------|------------|-----|--------------|

| 0  | 0              | 0          | 0   | 0            |

| l  | 0              | 0          | 1   | 0            |

| 0  | . 1            | 0          | 1 - | 0            |

| ١  | 1              | 0          | 0   | 1            |

| 0  | 0              | 1 1        |     | 0            |

| 1  | 0              | 1 1        | 0   | 1            |

| O  | <del> </del> 1 | 1          | 0   | -1           |

| ١. | ١              | 1 , (      | lı  | 1 1          |

Sn=abn + abn + c(ab + abn)

Sn=abn + abn + c(ab + abn)

Sn=abn 00 01 | C

To B. Rolanby Kribnantanbon

The andrust Ka (an + bn)

en regroupant an mari, or n'a pas le ou es clusif:

$r_n = a_n b_n + b_n r_{n-1} + a_n r_{n-1}$   $\Rightarrow r_n = a_n b_n + r_{n-1} - (a_n + b_n)$

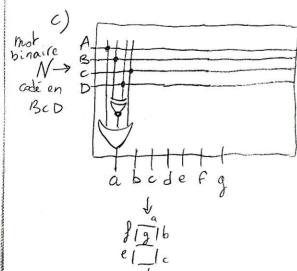

### transcodeur BCD. Affichage Thequents

un afficheur feut afficher des nombres affant de 0 à 9.

· Pour coder lo chiffres, it faut au moins 4 lets: 23=8 × 10

| TA       | B       | <u> </u> | + D         | Ţ          |            |                     |           |           |            |                     | 2         | 4=16; | > 10 |

|----------|---------|----------|-------------|------------|------------|---------------------|-----------|-----------|------------|---------------------|-----------|-------|------|

| -        | B       | 4        |             | N          | a          | Ь                   | C         | d         | e          | f                   | g         |       |      |

| 00000000 | 000000  | 000000-  | 0-0-0-0-0-6 | 0123456789 | 1011011111 | 7 1 7 7 7 7 6 7 7 1 | 110111111 | 101101101 | 1010001010 | 1 0 0 0 1 1 1 0 1 1 | 001111011 | •     |      |

| 1        | 0 0 1 1 | 0001     | 0-0-0-      | ABXDEF     |            |                     | (lan      | AR<br>AR  | CDIO       | 0 0                 | 1         | 10    | ľ    |

le segment Ma:

Representation symbolique:

# TP Electronique nº Corrigée Logique Combinatoire (2). Multiphereur-Démultiplexeur

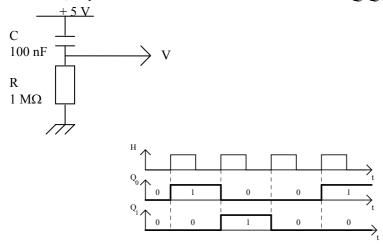

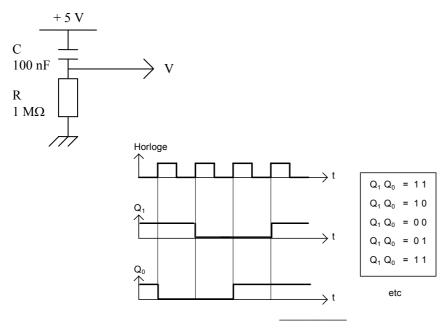

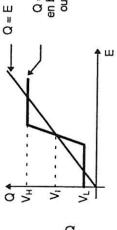

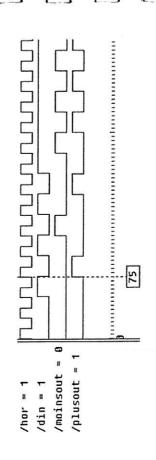

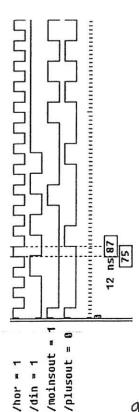

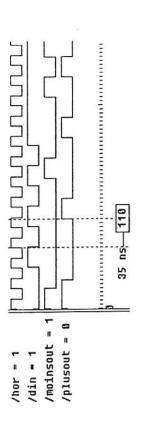

3. Etade théorique 3.0. Horlage;

\* Algine des leup: instant où inspasse de 0 à E: t = 0: conadrive  $= U_1$   $U_2 = E$  C se charge à E à havers R avecomme  $(.i.: u_e(0) = v_e(0))$   $I_1 = C$   $I_2 = C$   $I_3 = C$   $I_4 =$

de dine des temps : cholant où us posse de E à 0 : € t=0 : on a alors : U = U2

$$e^{t_1}$$

$$T_{H} = C \left|_{n} \frac{U_{2}(U_{1}-E)}{U_{1}(U_{2}-E)}\right|$$

or Rapport cyclique:

$$R_o = \frac{t_1}{T_H} = \frac{1}{2}$$

$\rightarrow \frac{\sum l_n \left(\frac{\upsilon_1 - \varepsilon}{\upsilon_2 - \varepsilon}\right)}{\sum l_n \left(\frac{\upsilon_2(\upsilon_1 - \varepsilon)}{\upsilon_1(\upsilon_2 - \varepsilon)}\right)} = \frac{1}{2}$

$$\rightarrow \left(\frac{U_{i}-E}{U_{\ell}-E}\right)^{\ell} = \frac{U_{\ell}}{U_{i}}\left(\frac{U_{i}-E}{U_{\ell}-E}\right) \rightarrow \frac{U_{i}-E}{U_{\ell}-E} = \frac{U_{\ell}}{U_{i}}$$

$$\longrightarrow \left[ U_{1}\left( U_{1}-E\right) =U_{2}\left( U_{2}-E\right) \right]$$

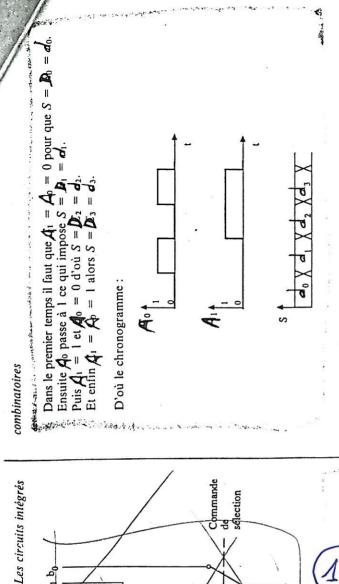

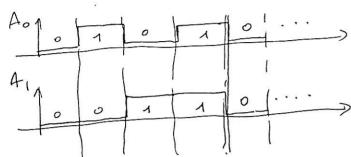

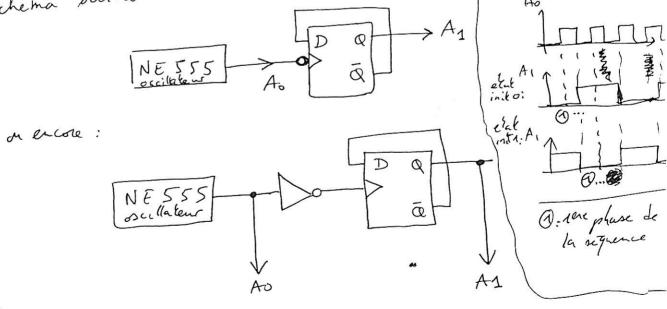

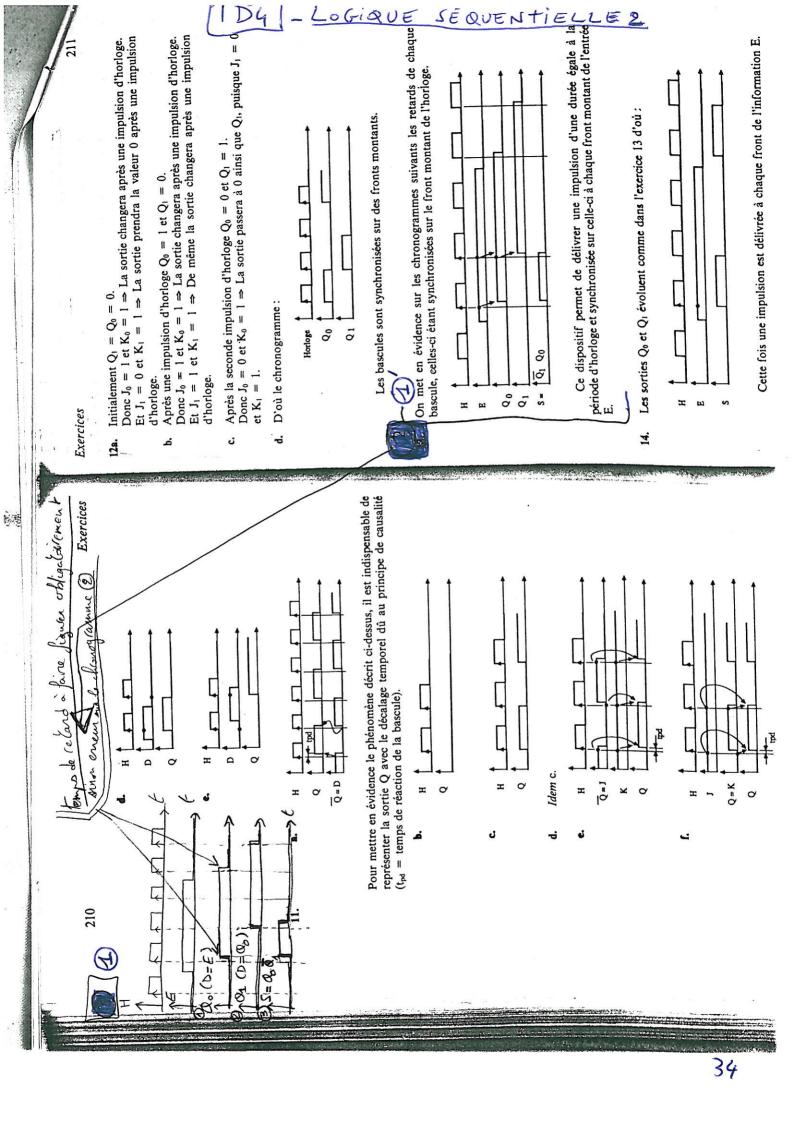

A desne la régience suivante pour les adresses A, A.o.:

A1: division par 2 de Ao.

Si Ao représente l'horloge de la basale Dégénérant An, il suffit

d'une part de complémenter l'horloge can on voit que le changement

d'état de An a liter pour un front descendant de Ao, et d'autre part

d'état de An a liter pour un front descendant de D, can à chaque

d'envoyer la sortie à de la bascul D en entrée de D, can à chaque

l'envoyer la sortie à de la bascul D en entrée de D, can à chaque

front descendant de l'horloge Ao, An change d'état on a donc le

front descendant de l'horloge Ao, An change d'étre pris quelcouque)

schéma suivant: (l'état initial de la bascule à pout être pris quelcouque)

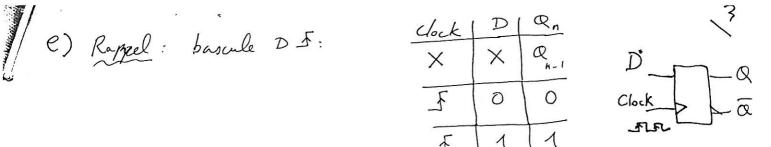

Table de vérité:

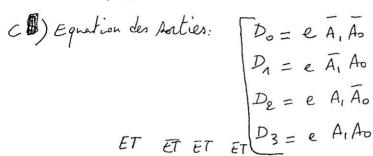

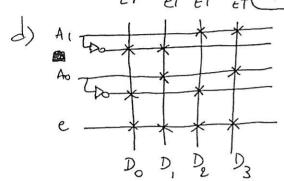

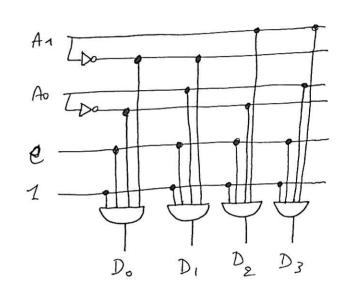

$$\begin{array}{c|c}

A_1 A_0 & D_1 \\

\hline

0 & 0 & D_0 = e \\

0 & 1 & D_1 = e \\

1 & 0 & D_2 = e \\

1 & 1 & D_3 = e

\end{array}$$

| 4. Et nde cofférimentale                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4. Et note vag ever de A. A. A. Do Les Let Lo chantent à la micre fréquence                                                                                                                  |

| , I/ DV                                                                                                                                                                                      |

| -10/                                                                                                                                                                                         |

|                                                                                                                                                                                              |

| 25 a) Or vérifie que si. A, Ao = 00, les LEDS L et Lo clignotent ensemble.  De multiplexens = 10,                                                                                            |

| =10,                                                                                                                                                                                         |

| 4.6.1. Affichage d'un digit:  4.6.1. Affichage d'un digit:  Avec le Transcodem TTL 7447, ma:  -pin 5: RBi = 1 (affichage de \$)  -pin 3: LT = 1 (test des sorties)  sorties complémentées 27 |

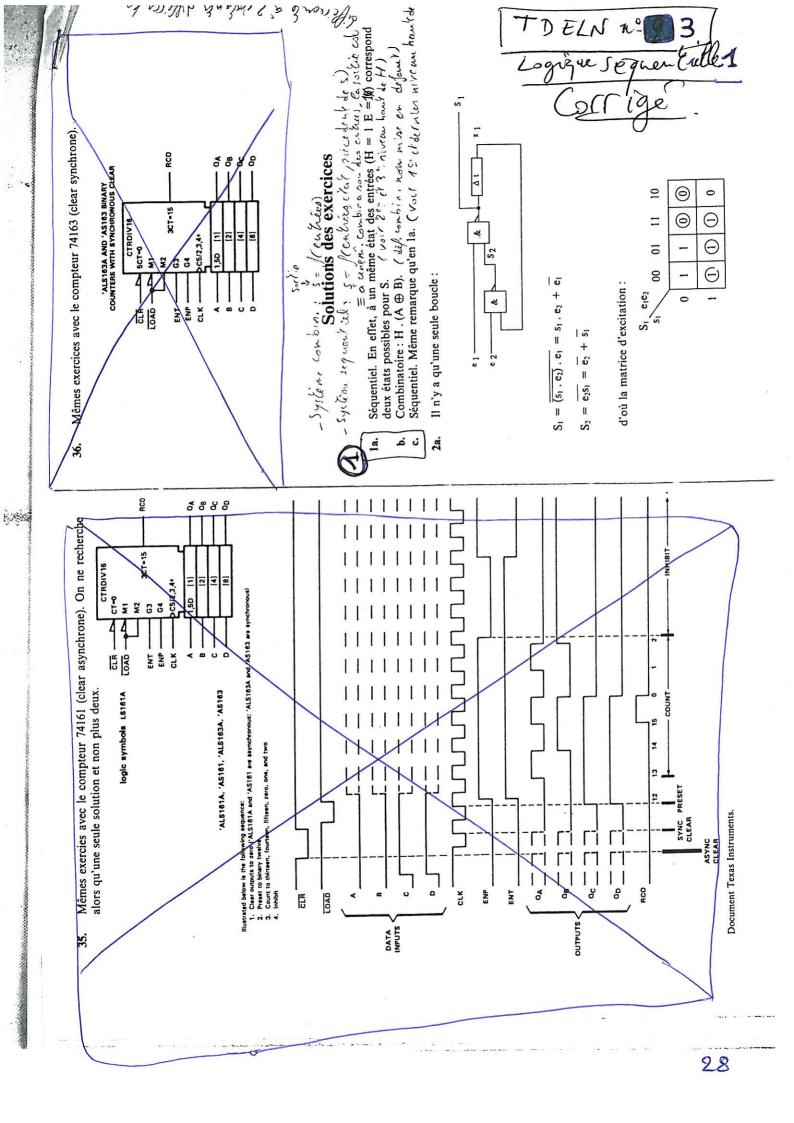

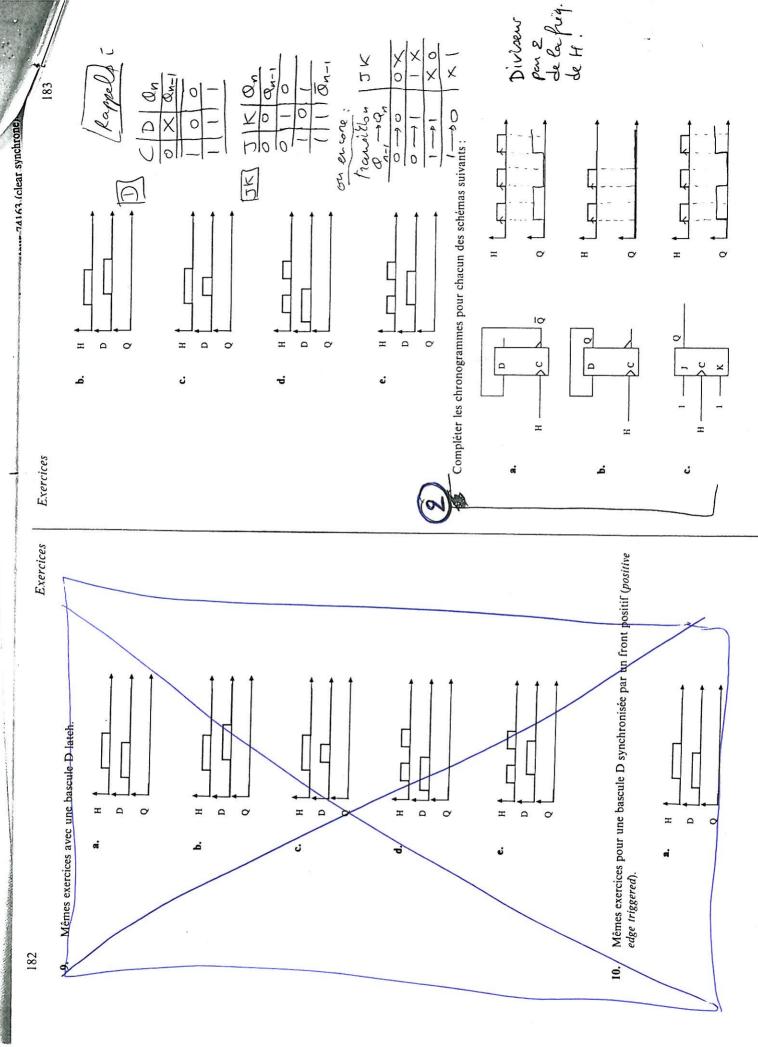

### TD 3 CORRIGE. LOGIQUE SEQUENTIELLE 1

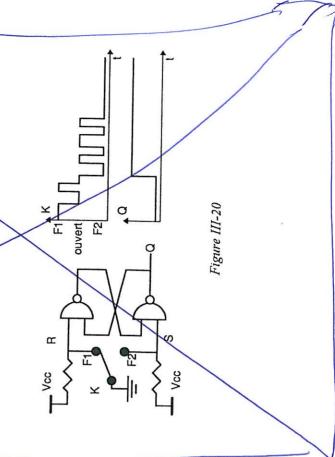

### 3. Bascule RS à entrées complémentées

### $\boldsymbol{x}$ m

#### **COMMENTAIRES**

| $x = \overline{R}$ | $y = \overline{S}$ | $m = Q_n$ | Fonction              |

|--------------------|--------------------|-----------|-----------------------|

| 1                  | 1                  | $Q_{n-1}$ | Mémorisation          |

| 0                  | 1                  | 0         | RESET (Mise à 0 de Q) |

| 1                  | 0                  | 1         | SET (Mise à 1 de Q)   |

| 0                  | 0                  |           | Combinaison interdite |

Application anti-rebond de la bascule RS

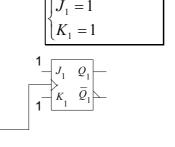

**4. Système séquentiel** L'état initial des bascules *JK* est l'état 0 :

1 TD 3 Corrigé.

### TD 3 ANNEXE CORRIGE. LOGIQUE SEQUENTIELLE 1

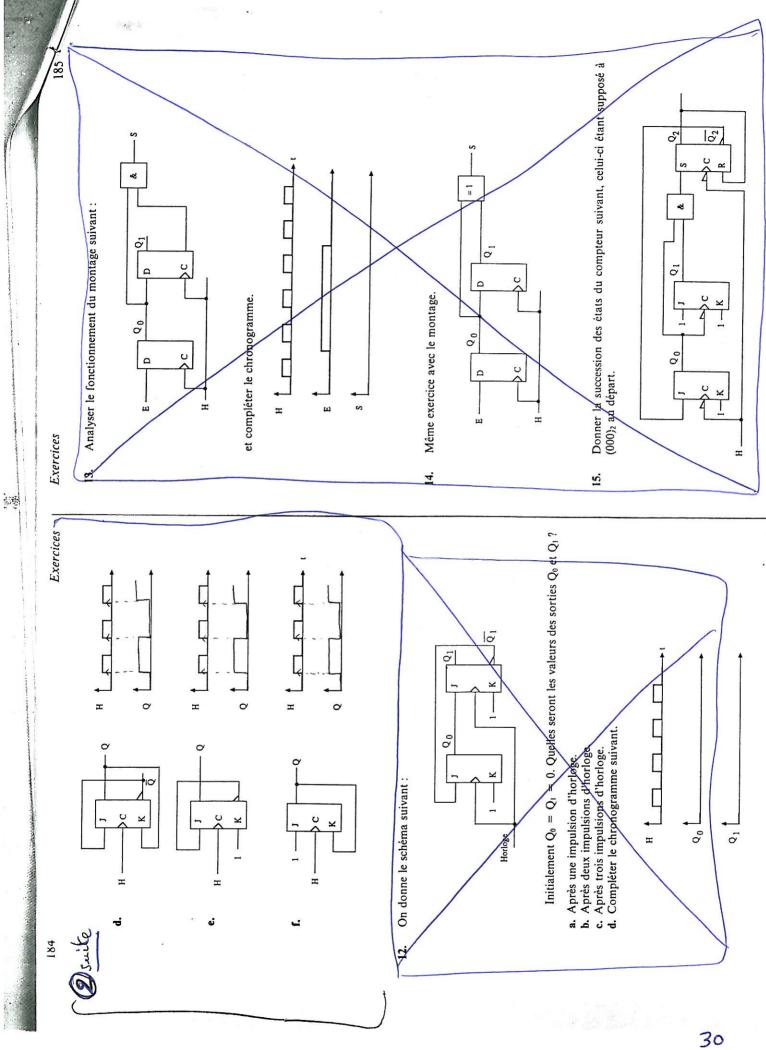

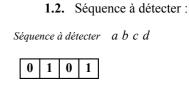

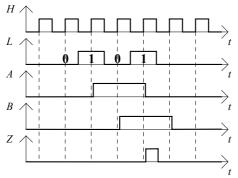

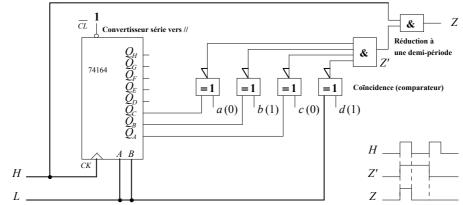

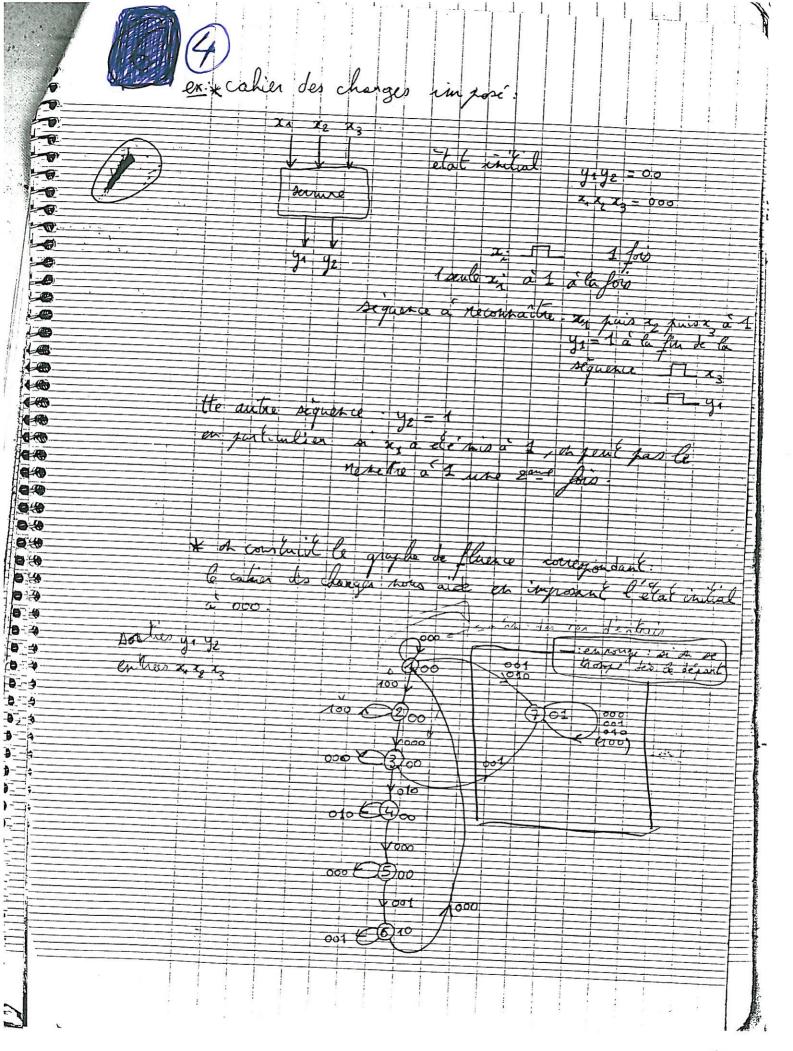

### 1. Détection synchrone d'une séquence (serrure électronique)

- 1. Solution à logique câblée (1)

- **1.1.** Les bascules ont un état initial bas : A = 0, B = 0

$Z = B L \overline{A} H$ Solution à logique sâblée (2)

2. Solution à logique câblée (2)

2.1.

2.2.

| Avantage 1                                                                                                                            | Avantage 2                                                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| La séquence à détecter est programmable, par exemple à l'aide de commutateurs (switches) mécaniques, et peut être modifiée à volonté. | • Le circuit peut être étendu à un nombre<br>quelconque de bits de la séquence à décoder, en<br>allongeant le registre à décalage et le circuit de<br>décodage. |

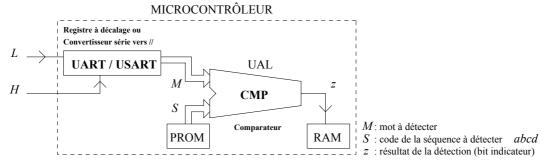

3. Solution à logique programmée

simple détection d'une séquence.

3.1.

3.2.

### Avantage • Le programme logé dans le microcontrôleur peut être modifié pour réaliser d'autres opérations que la

TD 3 Corrigé.

### TP 3 CORRIGE. LOGIQUE SEQUENTIELLE 1

### 3. Bascules JK (1)

L'état initial  $Q_1Q_0 = 00$  est obtenu (câblage uniquement) en envoyant V au Reset des bascules, le Set étant à 0: (en simulation, ne pas câbler les entrées R et S revient à initialiser à  $Q_1Q_0 = 00$ ).

- On a un compteur par 3:

$$Q_1Q_0 = \ 00 \ \rightarrow Q_1Q_0 = \ 01 \ \rightarrow \ Q_1Q_0 = \ 10 \ \rightarrow \ Q_1Q_0 = \ 00 \ \rightarrow \ \dots$$

Avec l'initialisation  $Q_1Q_0 = 11$ , on a :  $Q_1Q_0 = 11 \rightarrow Q_1Q_0 = 00 \rightarrow Q_1Q_0 = 01 \rightarrow Q_1Q_0 = 10 \rightarrow Q_1Q_0 = 00 \rightarrow ...$

### Le montage est autocorrecteur.

### 4. Bascules JK (2)

L'état initial  $Q_1Q_0=11$  est obtenu (câblage uniquement) en envoyant V au Set des bascules, le Reset étant à 0: (en simulation, ne pas câbler les entrées R et S revient à initialiser à  $Q_1Q_0=00$ ).

TP 3 Corrigé.

|                    | able des étals:                       |             |           |                                                   |               |              |             |                                                 |

|--------------------|---------------------------------------|-------------|-----------|---------------------------------------------------|---------------|--------------|-------------|-------------------------------------------------|

|                    | are ses etats.                        | 73722       | * * . `   |                                                   | 1 1900 1 1500 |              |             |                                                 |

|                    |                                       | 1 1         | 2 7       |                                                   | £ .           | 9, 98        | 1           | o cases                                         |

|                    |                                       | 2 3         | 2         |                                                   |               | 0 0          |             | des not                                         |

|                    |                                       | 3 3         | 4         |                                                   | 7             | 0 0          | de          |                                                 |

|                    |                                       | 5 5         |           |                                                   | 6             | 00           | (co         | es chaffe                                       |

|                    |                                       | 7 7         | 7   5     |                                                   | 16            | 10           | Ma          | porto que                                       |

|                    | 4 - 4                                 |             |           |                                                   |               | 01           |             | que hous                                        |

|                    | les autres                            | 6 et 7 1204 |           | a ax                                              | cim.          | an Eio       |             | 02                                              |

|                    | V: (A)                                | hour f      | E Ca      | equir                                             |               | 2            |             |                                                 |

|                    | 3                                     | 1 1 1       | Vou       | 7.4                                               | h res         | strik        | suis fal    | Can:                                            |

| 11-15-15 Pro- 11-1 | own delats                            | 12          |           | 2 3                                               | 2 1 2 X 2     | <b>*</b>     | 14.5        |                                                 |

|                    | i.                                    | 12          |           |                                                   |               |              |             |                                                 |

| G :                |                                       | 33          |           |                                                   |               |              |             | 20 13 20 15 15 15 15 15 15 15 15 15 15 15 15 15 |

| 8                  |                                       | 2.3         |           |                                                   | 大意义           |              |             |                                                 |

|                    |                                       | 2.5         |           |                                                   |               |              |             |                                                 |

| 9 H                | · · · · · · · · · · · · · · · · · · · | 34          |           |                                                   |               |              |             |                                                 |

|                    |                                       | 19.51       |           |                                                   |               |              |             |                                                 |

| 19                 | eq. m 1.3 eq                          |             |           | ndition                                           | 100           |              |             |                                                 |

| 1                  | Then 3                                | 4267 ha     | Marie S   | <del>                                      </del> |               | synlolis     | far w       |                                                 |

|                    | 1.2 1                                 | ush eg      | Dige      | 1 1 A                                             |               | eg a au      | ur ante     |                                                 |

| 2                  | Moh ey. ca                            |             | eg:       | ##                                                |               |              |             | - E                                             |

|                    | 215 men                               | as sporte   | a ce      | 9 1 l                                             | part es       | . de le      | rece qu     | els la                                          |

| 14 1               | 5 how ey.                             |             | then 7    | (A                                                | encado        |              |             | 100000                                          |

|                    |                                       |             | CLEWIT.   |                                                   | 1 la          | <b>1 3 5</b> | <del></del> | 2/1.                                            |

|                    |                                       | elala 2-3 e | misalant  |                                                   |               |              | 3           | X                                               |

|                    |                                       |             | miralente |                                                   |               | ##           |             |                                                 |

|                    |                                       |             |           |                                                   |               |              |             |                                                 |

|                    | - Anna Marian                         |             |           | - many                                            |               |              |             |                                                 |

Jo Ko 1 K 42 = Q2 41 Qi ex han electrique 3 boules: A, B, C go on pour solect P. School carier des charges T. : Contact le contret notwork to un poure orace Pet Q : you. log ques : devie Ticonlate alt. au nepos Jamage de tras il mercial > A, B, B, C

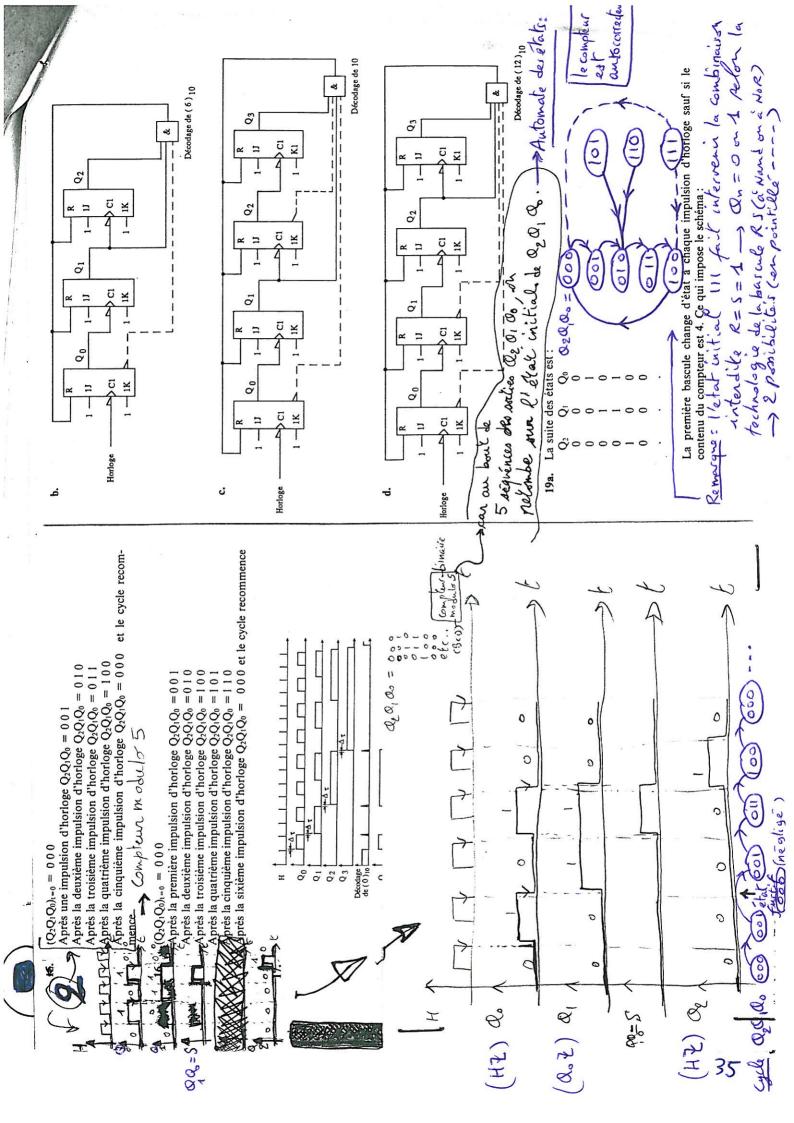

### TD 4 CORRIGE. LOGIQUE SEQUENTIELLE 2

### 3. Compteurs synchrones en anneau et non bouclé (Analyse)

### 1. Compteur en anneau à bascules JK

|    | Résultat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Commentaires                                                                                                                                                                                                                                                                                                                                        |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                     |

| 2. | DCBA<br>0001<br>1000<br>0100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Compteur modulo 4 câblé en registre à décalage                                                                                                                                                                                                                                                                                                      |

| 3. | Etat actuel         Etat futur           DCBA         DCBA             0000          0000              0000          0010              0010          0100              0010          0100              0100          1000              0101          1000              0101          1000              0001          1000              1000          0001              1010          0101              1010          0100              1101          0100              1101          0001              1111          0000 | Le tableau est beaucoup plus vite rempli si on a remarqué que le compteur est un registre à décalage propageant un 0 si l'entrée est un 0, et une inversion de l'état si l'entrée est un 1 : $ DCBA $ $ D'C'B'A' $ $ DCBA $ $ DCCBA $ $ DCCBA $ $ DCCC'B'A' $ $ DCCC'B'A' $ |

| 4. | NON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | L'état hors cycle $DCBA = 0000$ par exemple, ne peut être ramené dans le cycle normal : il boucle sur lui-même: $DCBA = 0000 \rightarrow 0000$ Autre contre-exemple : l'état hors cycle $DCBA = 0101$ ne peut être corrigé : il boucle sur lui-même : $DCBA = 0101 \rightarrow 1010 \rightarrow 0101$                                               |

### 2. Compteur en anneau à bascules D

|    | Résultat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Commentaires                                                                                                                                                                                                                                                                                                                            |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                         |

| 2. | DCBA<br>0001<br>0010<br>1000<br>0100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Compteur modulo 4<br>câblé en registre à décalage                                                                                                                                                                                                                                                                                       |

| 3. | Etat actuel         Etat futur           DCBA         DCBA           0000         0000           0010         0010           0011         0100           0100         1000           0110         1010           0111         1110           0101         1000           0111         1110           1001         001           1001         001           1010         0101           1011         0111           1100         1001           1101         1011           11101         1011           11111         11101           11111         11111 | Le tableau est beaucoup plus vite rempli si on a remarqué que le compteur est un registre à décalage parfait :  DCBA DCBA DCBA                                                                                                                                                                                                          |

| 4. | NON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | L'état hors cycle $DCBA = 0000$ par exemple, ne peut être ramené dans le cycle normal : il boucle sur lui-même: $DCBA = 0000 \rightarrow 0000$ Autre contre-exemple : l'état hors cycle $DCBA = 0011$ ne peut être corrigé : il boucle sur lui-même : $DCBA = 0011 \rightarrow 0110 \rightarrow 1100 \rightarrow 1001 \rightarrow 0011$ |

### 3. Compteur ouvert à bascules D

|    | Résultat                                              | Commentaires                                                                                                                                                                                                                      |

|----|-------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1. |                                                       |                                                                                                                                                                                                                                   |

| 2. | DCBA<br>0001<br>1000<br>0100                          | Compteur modulo 4<br>câblé en registre à décalage                                                                                                                                                                                 |

| 3. | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | Le tableau est beaucoup plus vite rempli si on a remarqué que le compteur est un registre à décalage parfait seulement sur les 3 variables $C, B, A$ mais pas $D: A$ devient $D_A = \overline{ABC}$ $D C B A$ $D C B A$ $D C B A$ |

| 4. | OUI                                                   | Il n'y a pas de contre-exemple : tout état hors cycle est ramené dans le cycle normal du compteur.                                                                                                                                |

### 4. Compteur synchrone (Synthèse)

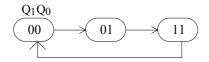

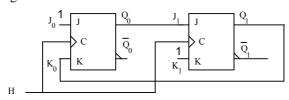

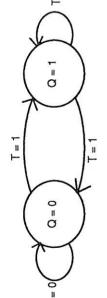

a) Cycle normal de comptage :  $Q_1Q_0 = 00 \rightarrow 01 \rightarrow 11 \rightarrow 00 \rightarrow ...$

Rappel: Table de transitions d'une bascule JK:

| Transition $Q_{n-1} \rightarrow Q_n$ | J K |

|--------------------------------------|-----|

| $0 \rightarrow 0$                    | 0 X |

| $0 \rightarrow 1$                    | 1 X |

| $1 \rightarrow 1$                    | X 0 |

| $1 \rightarrow 0$                    | X 1 |

. Table de Karnaugh établissant les entrées  $J_0K_0\, de$  la bascule de sortie  $Q_0$  :

| $Q_1$ $Q_0$ $Q_1$ | 0  | 1  |

|-------------------|----|----|

| 0                 | 1X | X0 |

| 1                 | XX | X1 |

$$\begin{cases} J_0 = 1 \\ K_0 = Q_1 \end{cases}$$

. Table de Karnaugh établissant les entrées  $J_1K_1$  de la bascule de sortie  $Q_1$  :

| $J_1K_1$ $Q_0$ $Q_1$ | 0  | 1  |

|----------------------|----|----|

| 0                    | 0X | 1X |

| 1                    | XX | X1 |

$$\begin{cases} J_1 = Q_0 \\ K_1 = 1 \end{cases}$$

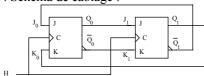

. Schéma de câblage :

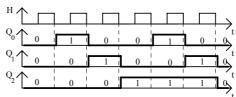

c) L'analyse (chronogramme) montre que l'état successeur de  $Q_1Q_0=10$  est  $Q_1Q_0=01$ :  $Q_1Q_0=10 \rightarrow 01$  Le compteur est donc **autocorrecteur**:

*d)* Si le compteur n'avait pas été autocorrecteur, le rendre autocorrecteur se ferait en reprenant la synthèse *a)* et en éliminant les choix *xx* effectués dans les tables de Karnaugh pour les forcer selon le cycle autocorrigé.

### TP 4 CORRIGE. LOGIQUE SEQUENTIELLE 2

### 3. Compteurs

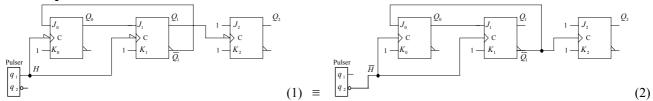

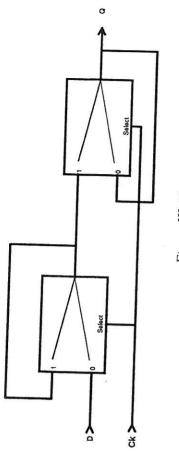

Le schéma initial (1) peut être remplacé par le schéma (2) identique, mettant en jeu des bascules JK > 0 edge triggered (4027). Si le choix du schéma (1) est fait, l'utilisation de bascules JK > 0 edge triggered (4027) implique d'intercaler avant chaque entrée d'horloge des bascules un circuit inverseur 4049 (même famille CMOS que les bascules JK).

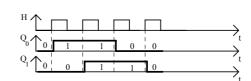

$$\begin{cases} J_0 = \overline{Q}_1 \\ K_0 = 1 \\ H \downarrow \end{cases} \begin{cases} J_1 = Q_0 \\ K_1 = 1 \\ H \downarrow \end{cases} \begin{cases} J_2 = 1 \\ K_2 = 1 \\ Q_1 \downarrow \end{cases}$$

Compteur modulo 6

Etat initial :

$$Q_2Q_1Q_0 = 000$$

Après la 1ère impulsion de H :  $Q_2Q_1Q_0 = 001$ Après la 2nde impulsion de H :  $Q_2Q_1Q_0 = 010$ Après la 3ème impulsion de H :  $Q_2Q_1Q_0 = 100$ Après la 4ème impulsion de H :  $Q_2Q_1Q_0 = 101$ Après la 5ème impulsion de H :  $Q_2Q_1Q_0 = 110$

Après la 6ème impulsion de H :  $Q_2Q_1Q_0 = 000$

... et le cycle recommence

### 4. Synthèse de Compteur 2 bits

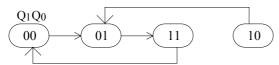

**Cycle voulu :**  $Q_1Q_0 = 00 \rightarrow 01 \rightarrow 11 \rightarrow 10 \rightarrow 00 \rightarrow ...$

Rappel: Table de transitions d'une bascule JK:

| Transition $Q_{n-1} \rightarrow Q_n$ | J | K |

|--------------------------------------|---|---|

| $0 \rightarrow 0$                    | 0 | X |

| $0 \rightarrow 1$                    | 1 | X |

| 1 → 1                                | X | 0 |

| 1 → 0                                | X | 1 |

. Table de Karnaugh établissant les entrées  $J_0K_0$  de la bascule de sortie  $Q_0$  :

| J <sub>0</sub> K <sub>0</sub> | _  |    |

|-------------------------------|----|----|

| Q <sub>1</sub> Q <sub>0</sub> | 0  | 1  |

| 0                             | 1X | X0 |

| 1                             | 0X | X1 |

$$\begin{cases} J_0 = \overline{Q}_1 \\ K_0 = Q_1 \end{cases}$$

. Table de Karnaugh établissant les entrées J<sub>1</sub>K<sub>1</sub> de la bascule de sortie Q<sub>1</sub> :

| $J_1K_1$ | _  |    |

|----------|----|----|

| $Q_1$    | 0  | 1  |

| 0        | 0X | 1X |

| 1        | X1 | X0 |

$$\begin{cases} J_1 = Q_0 \\ K_1 = \overline{Q}_0 \end{cases}$$

. Schéma de câblage :

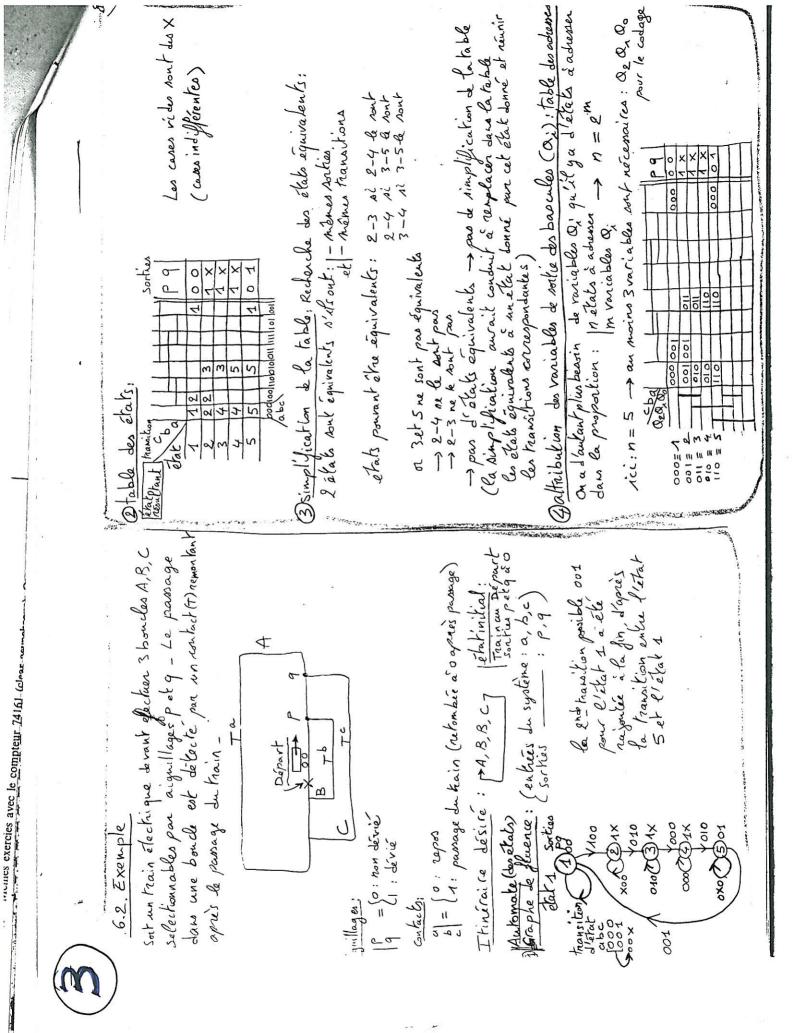

### 5. Séquenceur Train électrique

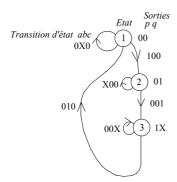

a) Automate des états correspondant à la trajectoire

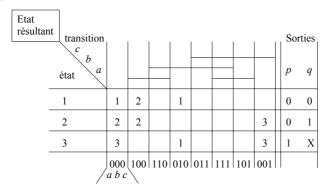

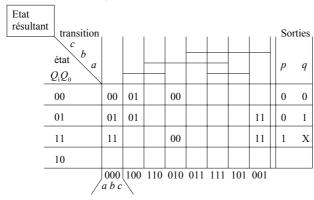

- b) Synthèse avec des bascules JK synchrones positive edge triggered, permettant de commander les aiguilleurs p et q

- Table des états

- Pas de simplification de la table des états (pas d'états équivalents)

- Variables de sortie des bascules

3 états  $\rightarrow$  2 variables  $Q_1Q_0$

### Electronique Numérique

- Tables de Karnaugh des bascules  $J_i K_i$

| $J_{_{0}}K_{_{0}}$ trans | ition        | l . | l   | l . | ı   | ı   | ı   |     | So | rties |

|--------------------------|--------------|-----|-----|-----|-----|-----|-----|-----|----|-------|

| état $Q_1Q_0$            | b a          |     |     |     |     |     |     |     | p  | q     |

| 00                       | 0X           | 1X  |     | 0X  |     |     |     |     | 0  | 0     |

| 01                       | X0           | X0  |     |     |     |     |     | X0  | 0  | 1     |

| 11                       | X0           |     |     | X1  |     |     |     | X0  | 1  | X     |

| 10                       |              |     |     |     |     |     |     |     |    |       |

|                          | 000<br>a b c |     | 110 | 010 | 011 | 111 | 101 | 001 |    |       |

Non simplification (car trop de variables pour appliquer la méthode de Karnaugh) :  $\begin{cases} J_0 = a\,\overline{b}\,\overline{c}\,\overline{Q}_1\,\overline{Q}_0 \\ K_0 = \overline{a}\,\overline{b}\,\overline{c}\,Q_1\,Q_0 \end{cases}$

| $J_1$ | $K_1$ transition                                                  |              |     |     | 1   |     |     |     |     | Sc | orties |

|-------|-------------------------------------------------------------------|--------------|-----|-----|-----|-----|-----|-----|-----|----|--------|

|       | $ \begin{array}{ccc} \text{état} & b \\ Q_1 Q_0 & a \end{array} $ |              |     |     |     |     |     |     |     | p  | q      |

|       | 00                                                                | 0X           | 0X  |     | 0X  |     |     |     |     | 0  | 0      |

|       | 01                                                                | 0X           | 0X  |     |     |     |     |     | 1X  | 0  | 1      |

|       | 11                                                                | X0           |     |     | X1  |     |     |     | X0  | 1  | X      |

|       | 10                                                                |              |     |     |     |     |     |     |     |    |        |

|       | /                                                                 | 000<br>a b c | 100 | 110 | 010 | 011 | 111 | 101 | 001 |    |        |

Non simplification (car trop de variables pour appliquer la méthode de Karnaugh) :  $\begin{cases} J_1 = \overline{a}\,\overline{b}\,c\,\overline{Q}_1\,Q_0 \\ K_1 = \overline{a}\,\overline{b}\,\overline{c}\,Q_1\,Q_0 = K_0 \end{cases}$

- Equation des sorties

$$\begin{array}{c|ccccc} p & q & & & & & \\ & Q_1 & & 0 & & 1 \\ \hline & 0 & & 00 & & 01 \\ \hline & 1 & & XX & & 1X \end{array}$$

$\begin{array}{c|cccc} p & q & Q_0 & 0 & 1 \\ \hline Q_1 & 0 & 0 & 1 \\ \hline 0 & 00 & 01 \\ \hline 1 & XX & 1X \\ \end{array}$  Après simplification :  $\begin{cases} p = Q_1 \\ q = Q_0 \end{cases}$

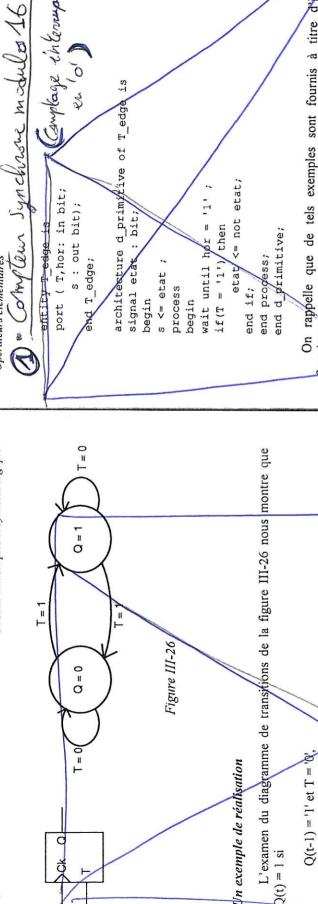

### TD 5 CORRIGE. VHDL

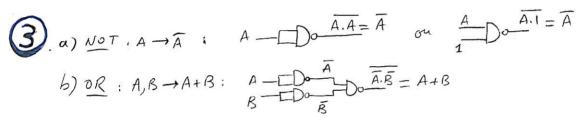

- **1. Programme VHDL des Opérateurs fondamentaux : NON, ET, OU** Voir livre VHDL (Meaudre & all ...).

- **2. Programme VHDL de l'Opérateur OU exclusif** Voir livre VHDL (Meaudre & all ...).

- 3. Programme VHDL d'un Multiplexeur  $2 \rightarrow 1$  Voir livre VHDL (Meaudre & all ...).

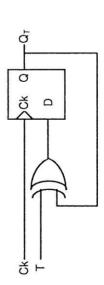

- **4. Programme VHDL d'une Bascule D latch** Voir livre VHDL (Meaudre & all ...).

-- operateur ou

Opérateurs élémentaires

Descriptions

50

W

@44-747: Ope a Few bondamentaux: NON,

20

ㅁ

NON

Figure III-5

Circuits numériques et synthèse logique

Description en VHDL

Des tautologies

Les exemples de code source VHDL ci-dessous ne nous apprennent rien sur les propriétés des opérateurs concernés, ils nous montrent l'aspect d'un programme VHDL et nous rappellent que les opérations NON, ET et OU sont définies sur les objets de type BIT comme sur ceux de type BOOLEAN, avec une convention logique positive ( $1 \equiv \text{TRUE}$ ,  $0 \equiv \text{FALSE}$ )

-- inverseur (ceci est un commentaire) PORT ( e : IN BIT ; -- les entrees ENTITY inverseur IS

s : OUT BIT ); -- les sorties

END inverseur;

ARCHITECTURE pleonasme OF inverseur IS BEGIN

de même ;

END pleonasme;

s <= NOT e;

PORT (el, e2 : IN BIT; -- operateur ET ENTITY et IS

BIT ); ruo : s END et;

ARCHITECTURE pleonasme OF et

s <= el AND e2; END pleonasme; BEGIN

ou encore:

6. VHDL Conuge

るのフ

On notera la structure générale d'un programme et le symbole « d'affectation » particulier aux objets de nature signal (s, e, e1, e2). La déclaration ENTITY correspond au prototype d'une fonction en C, elle décrit l'interaction entre l'opérateur et le monde environnant. La partie ARCHITECTURE du programme correspond à la description interne de l'opérateur, elle décrit donc son fonctionnement. Les mots clés du langage ont été mis en majuscule, c'est une IS ARCHITECTURE pleonasme OF ou s : OUT BIT ); PORT (e1, e2 : IN BIT; END pleonasme; s <= e1 OR e2; ENTITY ON IS END ou; BEGIN

Des affectations conditionnelles

habitude de certains, pas une obligation.

Dans les programmes qui suivent on voit apparaître la notion de « haut niveau» du langage. Des expressions purement booléennes sont utilisées pour décrire le fonctionnement d'un circuit. Ici elles traduisent strictement les tables de vérité, mais permettent évidemment des constructions beaucoup plus élaborées.

s : OUT BIT ); PORT ( e : IN BIT ; ENTITY inverseur IS END inverseur; -- inverseur

ARCHITECTURE logique OF inverseur IS s <= '1' WHEN (e = '0') ELSE END logique; BEGIN

de même :

s : OUT BIT ); PORT (el, e2 : IN BIT; -- operateur ET ENTITY et IS

ARCHITECTURE logique OF et END et; BEGIN

s <= '0' WHEN (e1 = '0' OR e2 = '0') ELSE '1'; END logique;

ou encore:

© меssои. La photocopie non autorisée est un délit.

61

```

s <= 0.0 WHEN (e1 = 0.0 AND e2 = 0.) ELSE 11;

ARCHITECTURE logique OF ou IS

BIT ;

s : OUT BIT );

PORT ( e1, e2 : IN

-- operateur OU

ENTITY on IS

END logique;

END ou;

BEGIN

```

# Des exemples de modèles comportementaux

Terminons cette première découverte de VHDL par deux descriptions purement comportementales des opérateurs ET et OU :

```

IF (e1 = '0' OR e2 = '0') THEN

ARCHITECTURE abstrait OF et IS

ENTITY et IS -- operateur ET

s : OUT BIT );

PORT (el, e2 : IN BIT;

<= '1';

s <= '0';

PROCESS (el,e2)

END IF;

END abstrait;

END PROCESS;

ELSE

END et;

```

ou encore:

```

PORT ( e : IN BIT VECTOR(0 TO 1) ; -- ATTENTION!!!

ARCHITECTURE abstrait OF ou IS

s <= 101;

s <= '1';

s : OUT BIT );

WHEN OTHERS =>

WHEN "00" =>

-- operateur OU

CASE e IS

PROCESS ( e )

ENTITY on IS

END ou;

BEGIN

BEGIN

```

END PROCESS;

END abstrait;

### Un peu d'algèbre N.2.2

Nous rappelons rapidement ici quelques propriétés élémentaires des opérateurs fondamentqux de la logique combinatoire. Le lecteur désireux de parfaire sa culture sur ce sujet pourra consulter un ouvrage de mathématiques, au chapitre qui traite de l'algèbre de Boole ou de l'algèbre des parties d'un ensemble? Parmi ces propriétés, les plus importantes, et de loin, dans les applications, sont les lois de De Morgan: ces deux lòis permettent de passer d'une convention logique à une autre,

Les démonstrations concernant l'algèbre de Boole peyvent toujours se faire, en dernier recours, par un examen des tables de vérité. Cette méthode, un peu lourde, doit être envisagée si des méthodes plus astucieuses ne sont pas trouvées; en tout état de cause, il n'est pas pensable de rester dans le doute en ce qui concerne un resultat de logique combinatoire L'intuition permet de gagner du temps dans l'obtention d'un résultat, son absence ne justifie pas le doute.

# Propriétés des opérateurs ET et OU

Associativité, commutativité

Associativité:

a \* (b \* c) = (a \* b) \* c, de même: a + (b + c) = (a + b) + c.

Commutativité:

a\*b/b\*a, et: a+b=b+a.

Un opérateuf, agissant sur deux opérandes, qui est associatif et commutatif peut être générálisé à un nombre quelconque d'opérandes, sans qu'il soit nécessaire de parenthéser les expressions, par exemple :

a+b+c+d+e est défini de façon univoque quel que soit l'ordre dans lequel on effectue les « calculs ».

Pratíquement cela signifie qu'il est possible de concevoir des opérateurs ET et OU à hombre arbitraire d'entrées (figure III-6) :

<sup>5</sup>Par exemple: J.C. BELLOC et P. SCHILLER: Mathématiques pour l'électronime Massan ASSON. La photocopie non autorisée est un délit

END CASE;

EXLUSIF permet de créer cette fonctionnalité, l'une de ses entrées est alors sortie d'un opérateur au moyen d'un «fusible» de polarité. L'opérateur OU considérée comme une entrée de donnée, l'autre comme une commande de polarité, (2) 54 -> 58: OU exclusif = Description structurelle conformément au schéma de principe de la figure III-13.

Figure III-13

### Descriptions en VHDL

VHDL connaît l'opérateur XOR comme primitive; les exemples qui suivent sont destinés à explorer, outre les propriétés de cet opérateur, des fonctionnalités du langage que nous n'avions pas abordées jusqu'ici

### Description structurelle

Ayant défini les opérateurs élémentaires ET, OU et NON comme précédemment, il est possible de les utiliser dans une construction plus complexe, comme le OU EXCLUSIF. L'exemple qui suit est, bien sûr, complètement académique, il est difficile d'imaginer plus compliqué pour réaliser un opérateur aussi simple!

ENTITY ouex IS -- operateur OU exlusif

s : OUT BIT );

END ouex;

PORT (a, b : IN BIT;

BEGIN -- les differents composants sont instancies ici use work.portelem.all ; -- rend visible le contenu de signal abar, bbar, abbar, abarb : bit; oul : ou port map (abbar, abarb, s); et1 : et port map (a,bbar,abbar); i2 : inverseur port map (b,bbar); et2 : et port map (b, abar, abarb); il : inverseur port map (a,abar); ARCHITECTURE struct OF ouex IS -- portelem

Opérateurs élémentaires

END struct;

préalable, créer et compiler le paquetage portelem et la description des opérateurs Pour que le programme précédent soit compris correctement, il a fallu, au élémentaires qui y sont décrits comme suit :

```

package portelem is

```

```

s : OUT BIT ); -- les sorties

PORT ( e : IN BIT ; -- les entrees

component inverseur

END component;

```

component et

```

s : OUT BIT );

PORT (el, e2 : IN BIT;

PORT (el, e2 : IN

END component;

END component;

component on

```

```

-- ce qui suit est la copie de programmes déjà vus

PORT ( e : IN BIT ; -- les entrees

ENTITY inverseur IS

end portelem;

```

```

ARCHITECTURE pleonasme OF inverseur IS

s : OUT BIT ); -- les sorties

END inverseur;

END pleonasme;

s <= NOT e;

BEGIN

```

```

s : OUT BIT );

PORT ( el, e2 : IN

-- operateur ET

ENTITY et IS

END et;

```

ARCHITECTURE pleonasme OF et s <= el AND e2; -- operateur OU END pleonasme; BEGIN

мезвои. La photocopie non autorisée est un délit.

ARCHITECTURE pleonasme OF on IS s : OUT BIT ); PORT (el, e2 : IN BIT; END ou;

ENTITY ou IS

s <= el OR e2; END pleonasme; BEGIN

### L'addition élémentaire

L'opérateur OU EXCLUSIF n'est autre que l'opérateur d'addition en base deux, le programme suivant en est la conséquence directe :

-- operateur OU exlusif

りした人

s : OUT INTEGER RANGE 0 TO 1 ); PORT ( a, b : IN INTEGER RANGE 0 TO 1 ; ENTITY onex IS

ARCHITECTURE arith of ouex is s <= a + b; END arith; END onex; BEGIN

### La comparaison

Si deux opérandes binaires sont différents le résultat de l'opérateur OU EXCLUSIF est '1':

parite := not parite;

end if;

END LOOP;

end process; s <= parite;

END parite;

if a(i) = '1' then

FOR i in 0 to 3 LOOP

begin

ARCHITECTURE compare of ouex is

END ouex;

s : OUT BIT );

PORT (a, b : IN BIT;

ENTITY onex IS

-- operateur OU exlusif

s <= '0' WHEN a = b ELSE '1';

BEGIN

END compare;

## Indicateur de parité impaire

Nous terminerons cette découverte du OU EXCLUSIF par sa généralisation comme contrôleur de parité d'un mot d'entrée :

-- operateur OU exlusif generalise

XUOO

мьзэом. La photocopie non autorisée est un délit.

PORT (a: IN BIT VECTOR (0 TO 3) s : OUT BIT );

ENTITY ouex IS

parite := not parite; ARCHITECTURE parite of ouex is variable parite : bit := '0'; if a(i) = '1' then FOR i in 0 to 3 LOOP end if; s <= parite; end process; END parite; process(a) END LOOP; begin BEGIN

Rien ne s'oppose, semble-t-il, à généraliser ce programme à un mot d'entrée de, mettons, 16 bits. Là se pose un petit problème : l'optimiseur du compilateur va exprimer la fonction obtenue comme somme (logique) de produits (logiques). Mais il y a 32 768 produits logiques dans un contrôleur de parité sur 16 bits (2<sup>15</sup>), d'où tenter de « réduire » les équations logiques sous-tendues par la boucle « for » pour les dangers des descriptions abstraites....

Une solution plus raisonnable, mais, il est vrai, non optimale du point de vue vitesse de calcul est8 :

ENTITY ouex4 IS -- le même que précédemment PORT ( a : IN BIT\_VECTOR(0 TO 3) ; s : OUT BIT );

ARCHITECTURE parite of ouex4 is

END ouex4;

variable parite : bit := '0';

process (a)

BEGIN

-- force la conservation des signaux intermédiaires s : OUT BIT VECTOR (0 TO 3); PORT (e : IN BIT\_VECTOR(0 TO 15); ENTITY ouex16 IS

\*Le lecteur est instamment convié à deseiner ייי مملمسم اعراب

END ouex;

59

58

-- le résultat complet s16 : OUT BIT); END ouex16;

SIGNAL inter : BIT\_VECTOR(0 TO 3); ARCHITECTURE struct OF ouex16 IS

PORT ( a : IN BIT\_VECTOR(0 TO 3) COMPONENT ouex4

s : OUT BIT ); END COMPONENT;

BEGIN

g1 : ouex4 port map (e(4\*i to 4\*i + 3), inter(i)); par16 : for i in 0 to 3 generate

g2 : ouex4 port map (inter,s16); end generate; s <= inter;

END struct;

On notera l'intérêt des boucles « generate » pour créer des motifs répétitifs.

## Le sélecteur, ou multiplexeur à deux entrées 111.2.5

...AUTREMENT. Mais quel est donc l'opérateur élémentaire qui, en logique ou multiplexeur. Nous donnons ci-dessous la description de sa version la plus simple, quand il n'y a que deux choix possibles dans l'alternative, mais il est bien De lecteur attentif n'aura pas manqué de remarquer que beaucoup de choses, en logique combinatoire, peuvent s'exprimer par des alternatives SI... ..ALORS... sûr possible de le généraliser pour représenter des choix multiples (IF... ...THEN... ELSIF... ELSIF... END IF, ou, CASE... IS WHEN... WHEN... END câblée, permet de matérialiser directement ce type de propositions? Le sélecteur,

### Description

### Principe général

Le sélecteur est construit comme un opérateur ou l'on sépare les variables d'entrée en deux groupes :

- Les entrées de données, qui sont en général issues d'autres fonctions;

- L'entrée de sélection, qui est une commande.

Prenons un exemple. Pour faire l'addition de deux chiffres, sans se poser de DCD, il faut commencer par faire l'addition de ces deux chiffres, sans se poser de l'addition de ces deux chiffres, sans se poser de l'addition de ces deux chiffres, sans se poser de l'addition de ces deux chiffres, sans se poser de l'addition de ces deux chiffres, sans se poser de l'addition de ces deux chiffres, sans se poser de l'addition de ces deux chiffres, sans se poser de l'addition de ces deux chiffres, sans se poser de l'addition de ces deux chiffres, sans se poser de l'addition de ces deux chiffres, sans se poser de l'addition de ces deux chiffres, sans se poser de l'addition de ces deux chiffres, sans se poser de l'addition de ces deux chiffres, sans se poser de l'addition de ces deux chiffres, sans se poser de l'addition de ces deux chiffres, sans se poser de l'addition de ces deux chiffres, sans se poser de l'addition de ces deux chiffres, sans se poser de l'addition de ces deux chiffres, sans se poser de l'addition de ces deux chiffres de l'addition de l'addit peuvent alors se produire

1. La somme est inférieure à 10 l'opération est alors terminée

Opérateurs élémentaires

2. La somme est supérieure ou égale à 10, ce résultat n'est alors pas correct en BCD. Il faut lui rajouter l'écart entre un nombre binaire sur 4 bits (0 à 15) et un chiffre décimal (0 à 9), soit 6.

Résultons ce qui précède sous forme d'un algorithme :

a et b sont les deux chiffres à additionner, s est le résultat. s = a + b

si s < 10 terminé

autrement s = s + 6

Une structure de la réalisation câblée de ce qui précède pourrait être celle de la figure IN-14 :

s = e0 \* sel + e1 \* sel selection sel ଚ e1 comparaison Figure III-14 e1>e2 10 1 e2 addition addition

Symbole et logigramme

dique les valeurs de l'entrée de sélection à côté des senté par un symbole qui inmentaire est souvent repréentrées de données respondantes (figure Le multiplexeur

Figure III-15

3 Milliplaxeur 2-1 = Description Konger lementale, Hel de donnéer et s'un Eurelle

Code source VHDL

Le multiplexeur à deux entrées est l'élément de base des descriptions dans des langages comme VHDL, nous n'en donnerons que quelques exemples

### Quelques tautologies

Nous retrouvons ici la définition même d'un multiplexeur.

: out bit); port (e0,e1,sel : in bit; entity sel is

end sel;

architecture pleonasme of sel is el when '1'; s <= e0 when '0', with sel select end pleonasme; begin

on :

: out bit); port (e0,e1,sel : in bit; entity selecteur is end selecteur; architecture procif of selecteur is if(sel = '0') then process (sel) begin

s <= e0; s <= e1; end process; end if; else

ou encore:

end procif;

out bit); : in bit; entity selecteur is port (e0,e1,sel end selecteur; architecture pleonasme of selecteur is

MUX8+1

Opérateurs élémentaires

s <= e0 when (sel = '0') else el; end pleonasme;

# Une autre façon de voir : les tableaux

VHDL connait les types structurés, la recherche d'un élément d'un tableau se traduit, en logique câblée, par un multiplexeur :

port ( e : in bit\_vector(0 to 1);

sel : in integer range 0 to 1; architecture vecteur of selecteur is : out bit); entity selecteur is s <= e(sel); end selecteur; end vecteur; begin

ou, en généralisant :

: in integer range 0 to 7; : in bit\_vector(0 to 7); architecture vecteur of selecteur is : out bit); entity selecteur is s <= e(sel); end selecteur; end vecteur; port (e sel

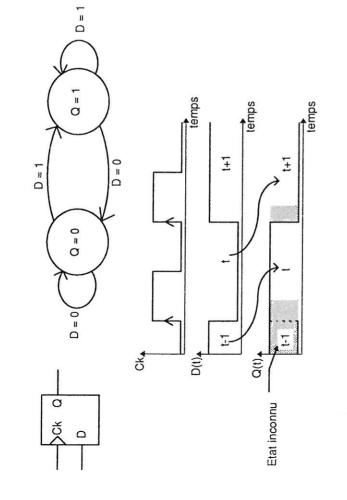

# III.3. Opérateurs séquentiels

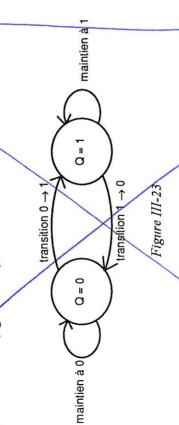

différencie un opérateur séquentiel d'un opérateur combinatoire réside dans la Nous avons déjà évoqué l'importance de la notion de mémoire, ce qui capacité du premier à « se souvenir » des événements antérieurs : une même combinaison des entrées, à un certain instant, pourra avoir des effets différents suivant les valeurs des combinaisons précédentes de ces mêmes entrées. Pour l'action des entrées est alors de provoquer d'éventuels changements d'état, la traduire cet effet de mémoire on introduit la notion d'état interne de l'opérateur, situation qui suit le changement de l'une d'elles dépend des valeurs des entrées et de l'état initial de l'opérateur ; si le nouvel état est différent du précédent on dit qu'il y a eu une transition. Premier aperçu

# Son contenu: une architecture

différentes pour la même déclaration d'entité. Une unité de conception est la Le fonctionnement interne d'un module, son corps, est précisé par une architecture associée à l'entité qui décrit l'aspect extérieur de ce module. Une architecture porte un nom, ce qui autorise la création de plusieurs architectures éunion d'une entité et d'une architecture.

### Syntaxe

èle. Cela signifie que les instructions d'une/architecture peuvent être écrites dans un ordre quelconque, le fonctionnement ne dépend pas de cet ordre entes parties d'un circuit coexistent et agissent simultanément. Il peut être un peu surprenant pour les programmeurs habitués des langages procéduraux L'architecture est divisée en deux parties ; yhe zone déclarative et une zone d'instructions, Ces instructions sont concurrentes, elles s'exécutent en paral-1'écriture. Ce point est simple à comprendre si on « pense circuits », les diffécomme C ou PASCAL, qui continuent \( \psi \) enser \( \times \) algorithmes séquentiels.

```

architecture architecture_name of entity_name is

end [ architecture ] [ architecture_name ] ;

architecture_declarative_par

architecture_statement_part

architecture_body ::=

begin

```

d'objets externes (composants d'une librairie, par exemple) utilisés dans le antes) locaux au bloc considéré. Élle permet également de déclarer des noms La zone déclarative permet de définir des types, des objets (signaux, conscorps de l'architecture.

### Exemples

Les trois exemples qui suivent correspondent aux trois exemples de déclarations d'entités donnés précédemment.

Un multiplexeur de quatre voies vers une voie:

```

..00.

:= "01"

:= "10"

:= "11"

11

6

6

6

6

: bit_vector(1 downto

: bit_vector(1 downto

: bit_vector(1 downto

: bit_vector(1 downto

architecture essai/of mux4_1 is

constant trois

constant zero

constant deux

constant un

begin

```

e<sub>0</sub> e1 II V sort <= sort process (e0,e1/e2,e3,sel) ٨ ٨ when zero case sel is when un begin

e2 e3 II V II V sort sort ٨ ٨ when trois when deux case ;

end process ; end essai ;

23

Notons en passant que <= représente l'opérateut d'affectation d'un signal.

Jn multiplexeur de dimension arbitraire : architecture essai of muxN\_1 is

sort <= entree(sel); begin

Un registre bidirectionnel de dimension arbitraire: end essai

signal temp : std\_logio\_vector(dimension - 1 downto 0) architecture essai of registre\_N is

r., donnee <= temp when diffection = '0' else (others => 'Z') process

if direction = '1' then wait until/hor = '1'; begin

temp/<= donnee ; end if

end process end essay

On distingue classiquement en VHDL trois styles de descriptions, qui peuvent être utilisés simultanément.

# (d) Description comportementale

JUX8-14

Une description comportementale (behavioral) se présente comme des blocs d'algorithmes séquentiels exécutés par des processus indépendants. Elle peut traduire un fonctionnement séquentiel ou combinatoire du circuit modélisé. Nous expliciterons ce point en détail dans la suite.

Un simple multiplexeur deux voies vers une voie peut être décrit par un algorithme qui reproduit son comportement:

architecture comporte of mux2\_1 is sort : out bit ) port(e0,e1 : in bit sel: in bit; process (e0,e1,sel)<sup>8</sup> entity mux2\_1 is end mux2\_1 ; begin

24